บทความนี้จะสอนวิธีออกแบบ Single stage CMOS Opamp โดยจะต่อวงจรเป็นแบบ Symmetrical CMOS OTA (Operational Transconductance Amplifier) ร่วมกับการใช้ Cascode MOS current mirror เพื่อทำให้เราได้อัตราขยายที่สูง

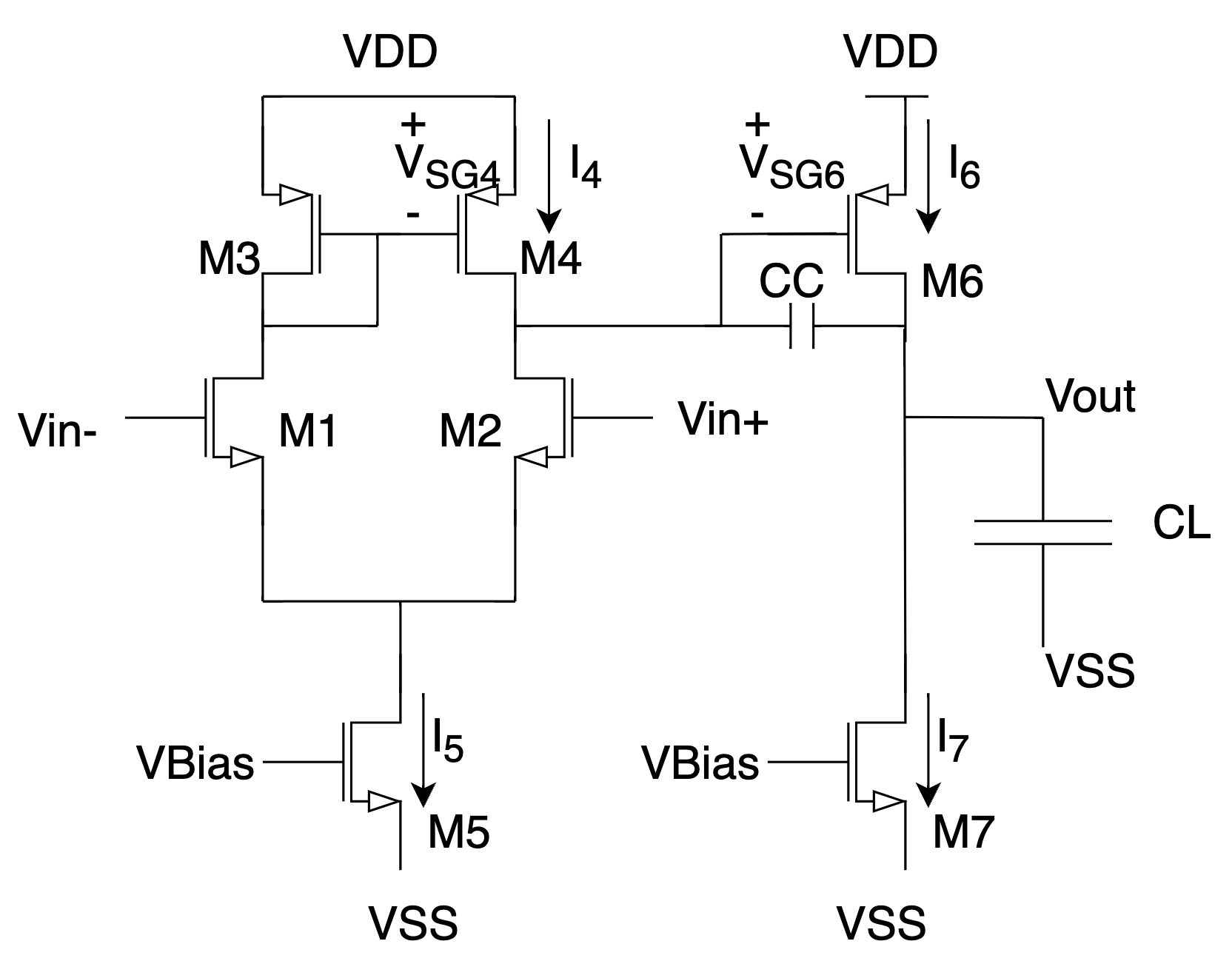

หากเราเทียบกับวงจร Opamp ที่ออกแบบในบทความที่แล้ว โดยมีลักษณะการต่อวงจรแบบ 2-stage Single ended opamp ดังรูปข้างล่าง เราจะเห็นว่าตัววงจรมีข้อจำกัดโดยเราต้องออกแบบให้ Vdsat4 = Vdsat 6 เพื่อให้กระแส I1 และ I2 มีค่าเท่ากันเพื่อไม่ให้เกิด Systematic offset

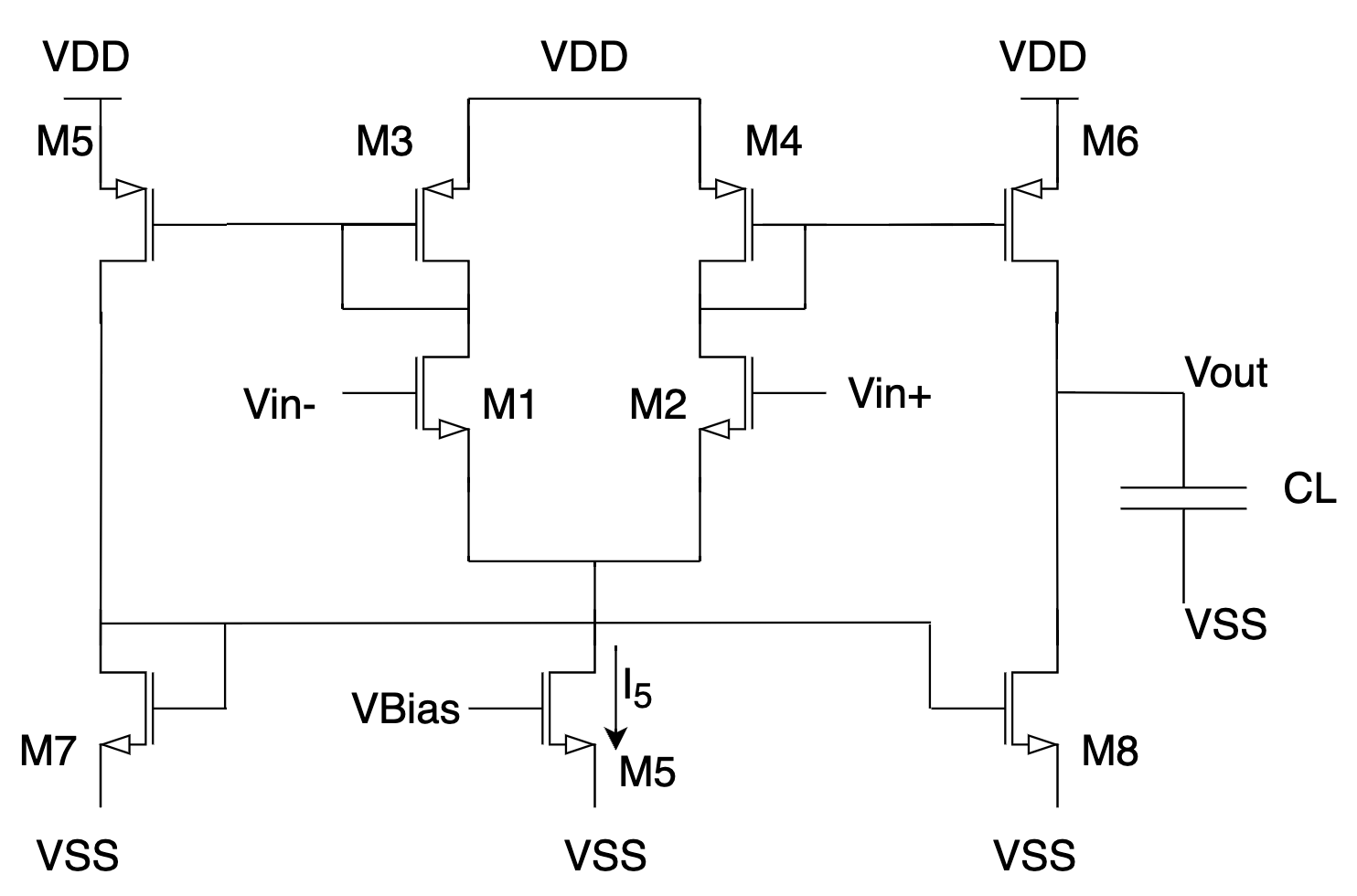

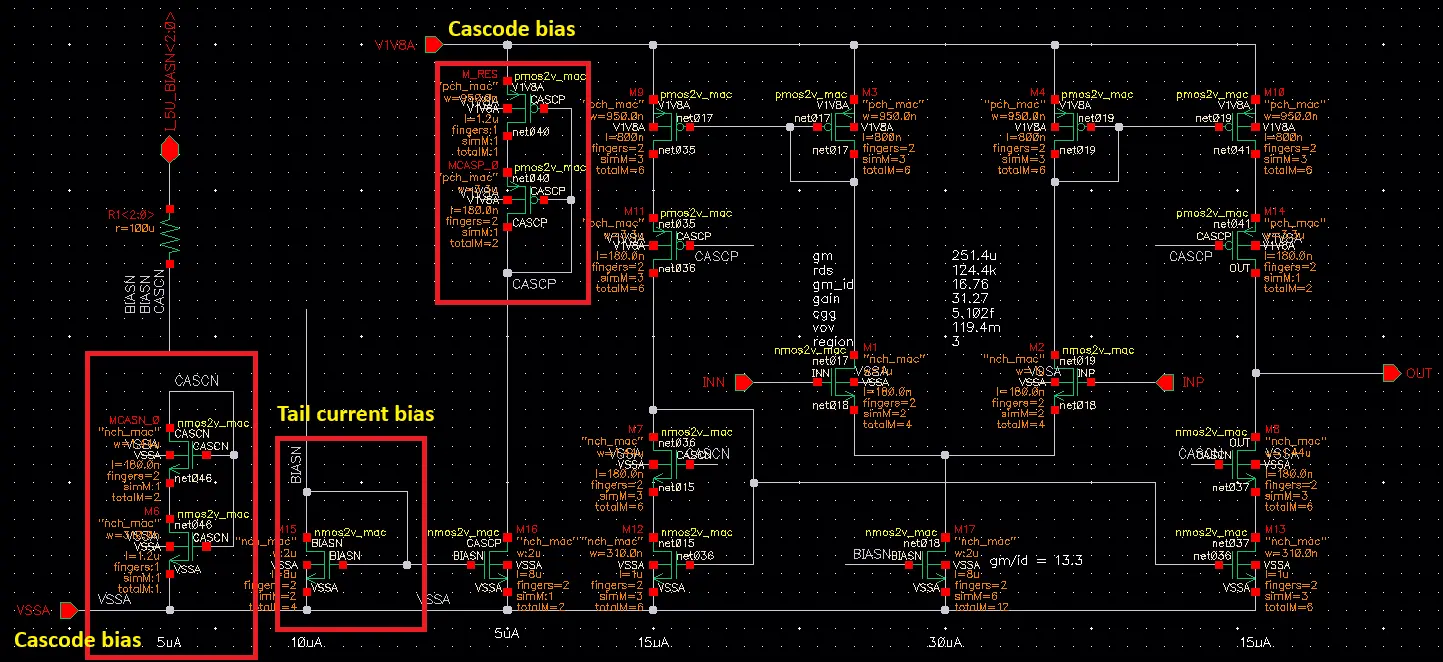

วงจร Symmetrical OTA ที่ใช้จะมีลักษณะดังรูปจะมีข้อดีเมื่อเปรียบเทียบกับ 2-stage single ended Opamp คือการมี Vdsat4 = Vdsat3 ซึ่งทำให้กระแสมีความสมมาตรและทำให้วงจรไม่มี Systematic offset นอกจากนี้ เรายังสามารถออกแบบให้ M8 และ M6 มีค่า Vov ที่สูงเพื่อลดผลของ random offset ที่เกิดจาก current mismatch อีกด้วย

โดย Open loop gain ของวงจร Symmetrical OTA จะมีค่าเป็น

\frac{Vo}{Vin} = gm_2 \cdot r_{o8} \|| r_{o6}

และมีค่า UGBW เป็น

f_{UGBW}=\frac{gm_2}{2\pi\cdot C_L}

เราจะเห็นว่าวงจร Sysmetrical OTA เป็นวงจรที่มีเพียง 1 pole ซึ่งจะมาจาก Loading capacitor CL และ Rout ดังนั้นเราจึงไม่จำเป็นต้องกังวลถึงเรื่อง Stability ของวงจรเมื่อเราต่อวงจร Opamp เพื่อใช้เป็นวงจรขยายแบบป้อนกลับ (Negative feedback) อย่างไรก็ตาม วงจรดังกล่าวยังมี pole อื่นๆแฝงเข้ามา โดย pole หลักจะมาจาก M3,4 และ M7 โดยจะมีค่าประมาณ gm/Cgg โดย Cgg จะเป็น parasitic capacitance ที่ gate ของ Transistor ดังนั้น เราไม่สามารถเลือกความถี่ UGBW ที่สูงเกินไปได้ เพราะสุดท้ายแล้ววงจรจะถูกจำกัดด้วย Ft (Transit frequency) ของ Transistor M3,4,7 ที่เราเลือก

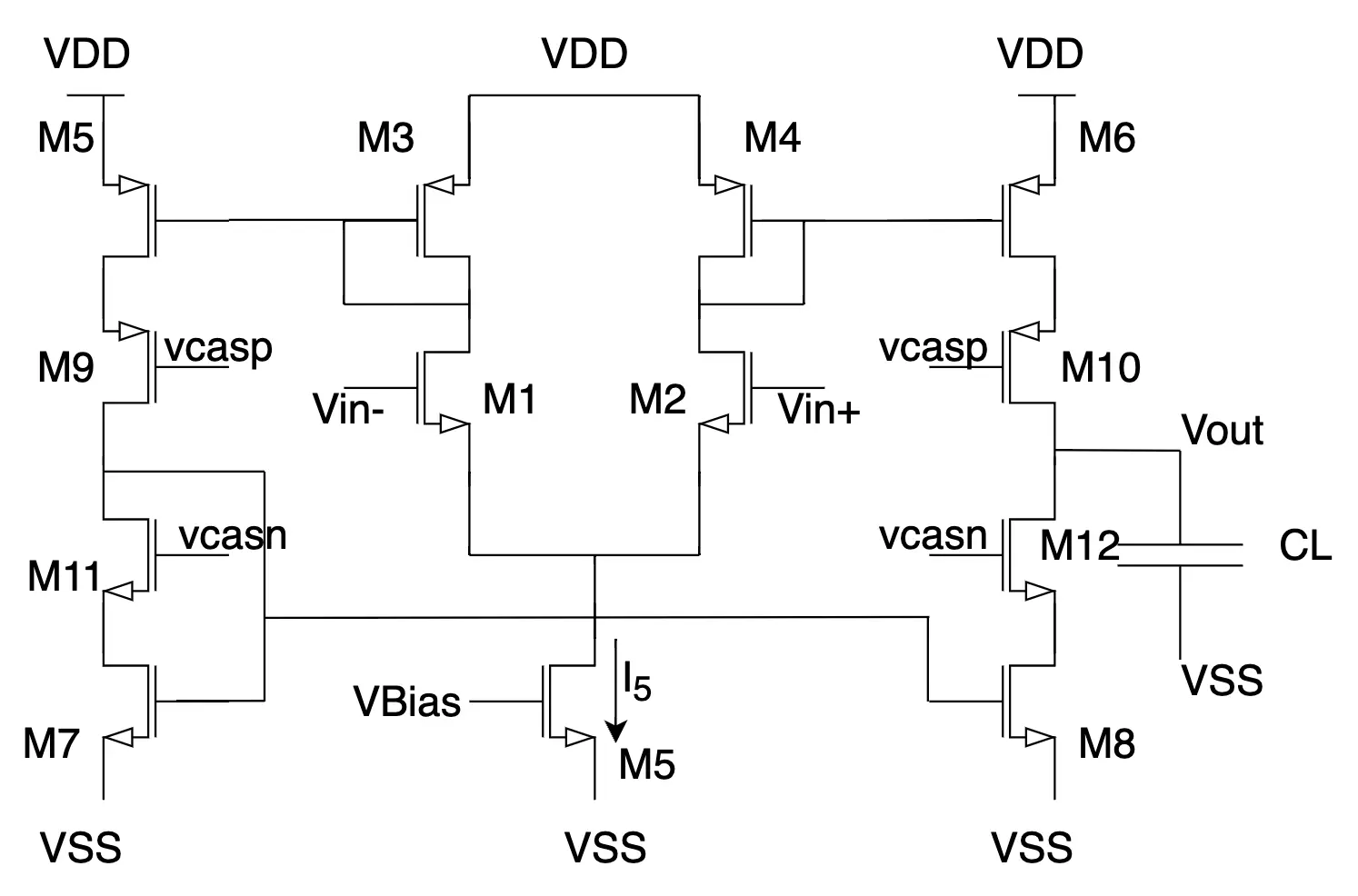

หากเราต้องการออกแบบวงจร Opamp ด้วยการต่อวงจรแบบ Symmetrical OTA แบบ 1 Stage เราจะได้ Opamp ที่มีกำลังขยายที่ไม่สูงนัก และอาจทำให้สูงได้ยากหากเราต้องออกแบบให้วงจรมีแบนด์วิดที่กว้าง สามารถทำงานที่ความถี่สูงได้ เนื่องจากการออกแบบให้วงจรมีค่ากำลังขยายที่สูงจะมาพร้อมกับการเลือก Rout ที่สูง ซึ่งหมายความว่าเราต้องเลือกค่า L ของ Transistor ที่มีขนาดใหญ่ส่งผลให้ non-dominant pole ของ Opamp (ซึ่งหลักๆจะมาจาก Cgg ของ M7) มีค่าที่ใกล้เคียงกับ UGBW จนทำให้ Phase margin มีค่าที่ต่ำเกินไป ดังนั้นหากเราต้องการออกแบบให้วงจรมีกำลังขยายที่สูง (เช่น 60dB) พร้อมกับมีช่วง Bandwidth ที่สูง (>10MHz) เราอาจต้องปรับเปลี่ยนตัววงจรเล็กน้อย โดยเราจะเพิ่ม Cascode Transistor เข้าไปที่ส่วนของ Rout ของ วงจรดังรูป (ดูวิธีออกแบบ Cascode Current Mirror)

การเพิ่ม Cascode Transistor M9, 10, 11 และ 12 จะช่วยเพิ่มความต้านทานของวงจร Opamp ซึ่งจะส่งผลให้เราสามารถเลือกใช้ขนาดของ Transistor ที่เล็กลงได้ เพื่อให้ non-dominant pole อยู่ที่ความถี่สูง ห่างจาก UGBW นั่นเอง โดย Rout ใหม่ที่เราได้จะเป็น

r_{op}\approx gm_9\cdot r_{o9} \cdot r_{o5}

r_{on}\approx gm_9\cdot r_{o9} \cdot r_{o5}

r_{out}=r_{op}\|| r_{on}

เราจะทำการออกแบบ Symmetrical OTA โดยกำหนด Design specification ดังนี้:

Open loop gain 60dB

UGBW 30MHz

Loading capacitor 1pF

Output swing 400mV - 1.4V (Vdd=1.8V)

Slew rate 30MV/s

(อ่านวิธีออกแบบ Design specification ได้ที่นี่)

และเราจะใช้หลักการ MOS Characterization ที่เคยเสนอในบทความก่อนหน้า

เราเริ่มต้นเลือกกระแส I5 จาก Slew rate ด้วยสมการ

SR=I_d/C_L

I_d=SR\cdot C_L=30MV/s \cdot 1pF=30uA

ดังนั้นเราจะเลือก I5 อยู่ที่ 30uA

หากเราต้องการออกแบบให้ Opamp มี Slew rate ที่สูง เราสามารถเพิ่มอัตราส่วนของ W6/W4 ให้สูงขึ้นได้ เพื่อลดความจำเป็นของการใช้ Tail current ที่สูงเกินไป แต่ในตัวอย่างนี้เราจะออกแบบให้กระแส I4 และ I6 มีอัตราส่วนเป็น 1:1

เราเริ่มจากการหาค่า gm ที่จะทำให้เราได้ UGBW > 30MHz ด้วยสมการ

f_{UGBW}=\frac{gm}{2\pi C_{L}}

gm\geq 188\mu S

และ

gm/I_d\geq 188\mu S / 15\mu A\geq12.5

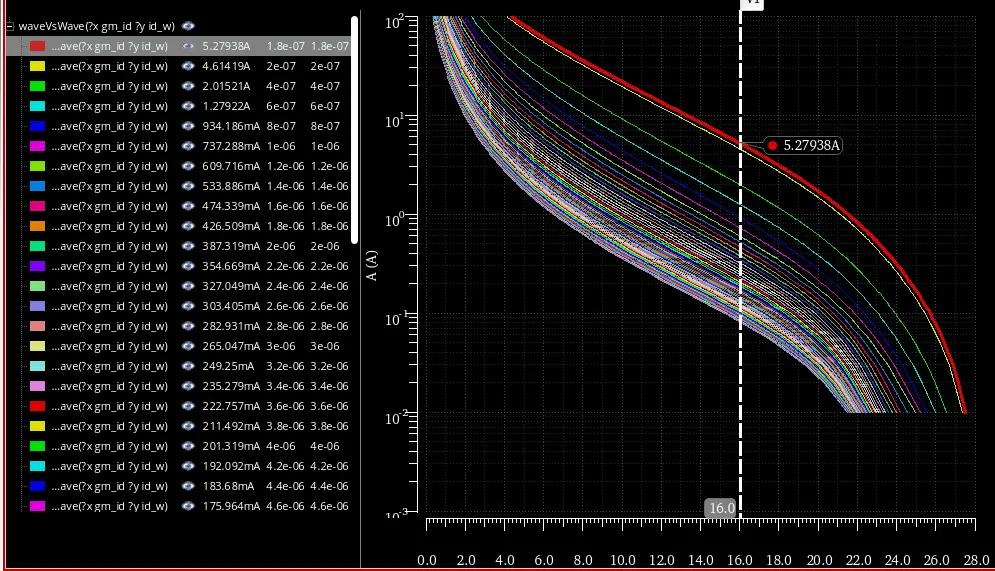

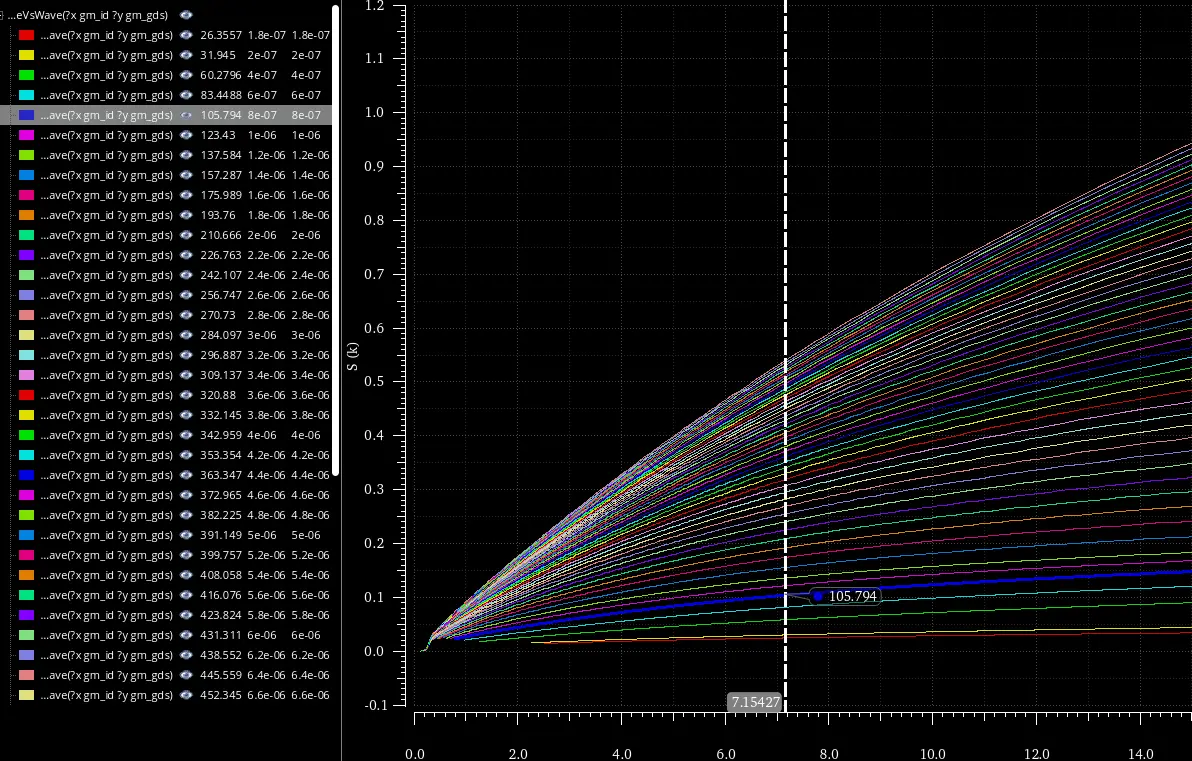

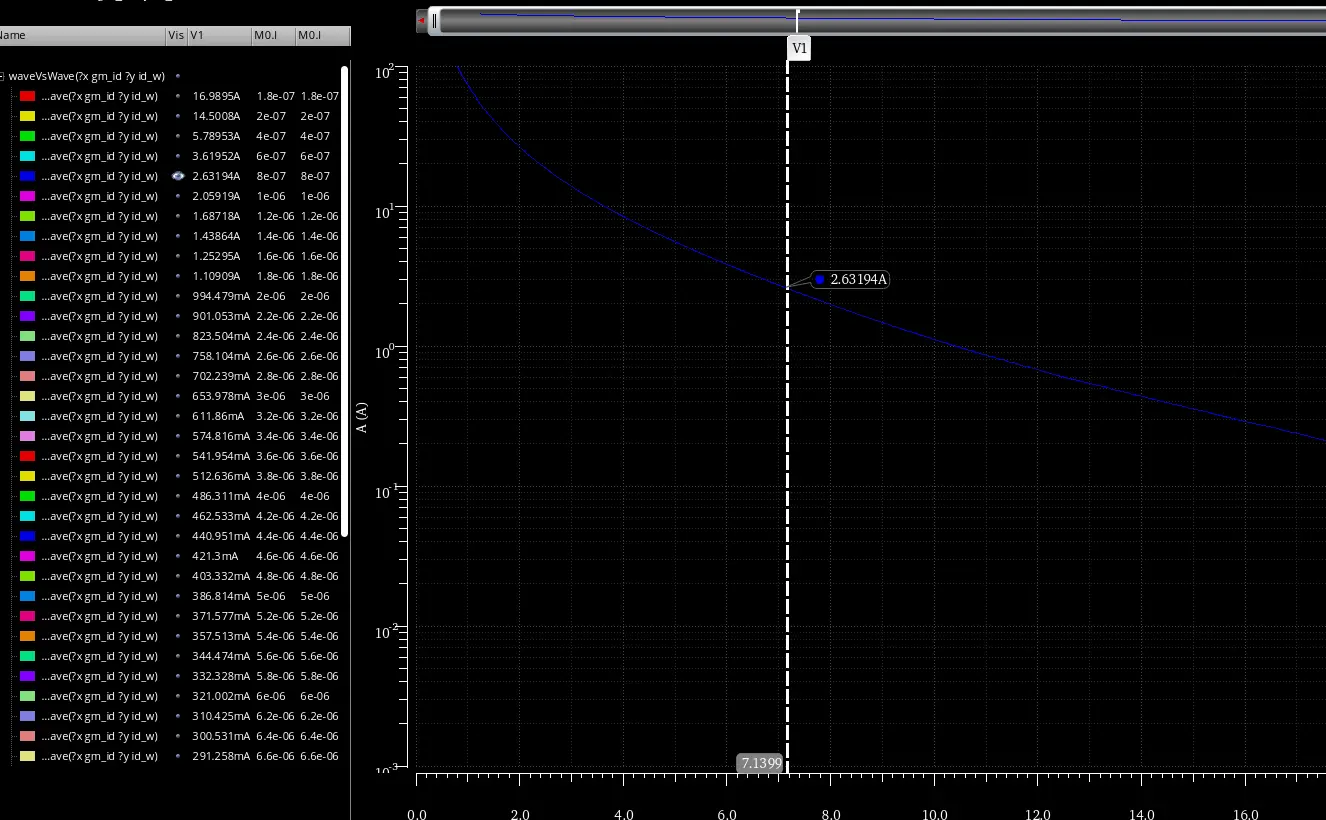

เราจะเลือก gm/Id = 16 เพื่อลด Random mismatch (อ่านบทความเพิ่มเติม) และเราจะเลือก L=180n เราจะได้ W จากกราฟ Current density เป็น I/W=5.28 ⇒ W≥2.54u

จะเห็นว่าเราในครั้งแรก เราได้เลือก W=2.54um และ L=180nm เพื่อให้ได้ gm และ gm/Id ที่ต้องการ อย่างไรก็ตาม ค่า W และ L จะมีค่าที่เล็กเกินไปซึ่งจะส่งผลให้เกิด random mismatch เราสามารถเพิ่มค่า W และ L ด้วยอัตราส่วนที่เท่ากัน เพื่อคงค่า gm ให้เป็นค่าเดิมได้ เช่นเพิ่ม W และ L เป็น 4 เท่าจากเดิม นอกจากนี้เรายังสามารถ optimize วงจรเพิ่มเติมได้ภายหลังจากการออกแบบด้วยการ simulate DC mismatch เพื่อหา offset contribution ของ Transistor ในแต่ละตัว และปรับปรุงขนาดของ Transistor ในภายหลัง (จะไม่แสดงในตัวอย่างนี้)

จาก W และ L ที่เลือก (เพิ่มเป็น W=4um เนื่องจากต้องการแบ่งออกเป็น m=2 และ f=2) เราจะได้ gm=251uS

จากนั้นเราจะเลือก Rout เพื่อให้ได้ Av=60dB จาก

A_v=gm\cdot R_{out}

R_{out}=10^{(60/20)}/251\mu=3.98M\Omega

เราจะออกแบบให้ rop และ ron มีความต้านทานอยู่ที่ประมาณ 9MOhm เพื่อให้ได้ rop||ron≥3.98MOhm

จาก rout ที่ต้องการให้มีค่าเป็น 9MOhm โดยมีกระแสไหล 15uA และมี Vdsat รวมกันไม่เกิน 400mV

เราจะเริ่มจากการเลือก Vov ของ Current Mirror MOS M5 (และ M6) ให้มีค่าเป็น Vov=280mV ดังนั้นเราจะได้

gm/id=\frac{2}{V_ov}=7.14

จากนั้น เราจะต้องเลือก gm/Id ของ Cascode MOS M9 (และ M10) ให้มีที่ค่าสูงเพื่อให้ได้ gm ที่สูงเป็น gm/id=20 ซึ่งเราจะได้ Vov อยู่ที่ 100mV เมื่อรวมค่า Vds แล้วจะได้ค่าไม่เกิน 400mV ตาม Design specification

ดังนั้น เราจะได้ gm cascode MOS เป็น

gm_{cascode}=(gm/id)\cdot I_d=20\cdot 15\mu A=300\mu S

จากนั้นเราจะสามารถเลือกค่า Rout ของ Mirror MOS และ Cascode MOS ได้ โดยเราจะเลือกให้ Rout Mirror MOS มีค่าสูงกว่า เนื่องจากเราต้องการให้ L ใน MOS mirror มีขนาดใหญ่เพื่อให้มี current matching ที่ดี ดังนั้นเราจะเลือก R MOS Mirror อยู่ที่ 500kOhm เราจะได้ R ของ Cascode เป็น

r_{cascode}\approx r_{o}/\left( gm_{cascode}\cdot r_{mirror} \right)=60kOhm

หากเราพิจารณาการออกแบบความต้านทานของ Current mirror ด้วยการใช้วงจร Cascode current mirror เราจะเห็นว่าเราสามารถออกแบบให้ได้ Rout ที่สูงเกือบถึง 10MOhm โดยใช้ Transistor ที่มี Rout ที่มีค่าที่ไม่ใหญ่มากนัก ซึ่งจะทำให้ขนาดของ Transistor มีขนาดที่ไม่ใหญ่จนเกินไป ทำให้ pole ที่เกิดขึ้นอยู่ที่ความถี่ที่สูงมากนั่นเอง

หลังจากที่เราได้ Rout, gm/id และ gm ของ Transistor M5 และ M9 แล้ว เราก็สามารถหาค่า W และ L ได้ง่ายด้วยวิธีการดูกราฟ Lookup Table ตัวอย่างเช่นการหา W และ L ของ M5

เราเริ่มจากการหาค่า Intrinsic gain เป็น

gm/gds=gm\cdot rds=107\mu S\cdot 500k\Omega=53.6

ทำให้เราสามารถเลือกค่า Length ของ Transistor จากกราฟ Intrinsic Gain ได้ดังรูป

เราจะได้ L=800nm (เลือกเผื่อไว้ เพราะ 800nm ที่ gm/I=7.14 ถือว่ายังมีขนาดที่เล็กพอสมควร)

จากนั้นเราสามารถหาค่า Width ได้โดยเริ่มจากการหาค่า gm เป็น

gm=(gm/id) \cdot I_d=7.14\cdot 15\mu A=107uS

เราจะได้ Width จากกราฟ Current density เป็น Id/W=2.63 ซึ่งทำให้เราได้ Width=5.7um

จากนั้นเราจะทำการออกแบบ Width และ Length ของ M9 ด้วยวิธีเดียวกัน เราจะได้ L=180nm และ W=19.8um

หลังจากเราได้ค่า W และ L ของ PMOS Cascode Current Mirror แล้ว เราจะต้องออกแบบวงจรไบอัสแรงดัน เพื่อจ่ายเป็นแรงดัน Cascode voltage ให้กับ Gate ของ Cascode Mirror โดยเราได้อธิบายตัวอย่างการออกแบบแล้วในบทความนี้

หลังจากที่เราออกแบบ PMOS current mirror เราก็สามารถออกแบบ NMOS current mirror ได้โดยใช้วิธีเดียวกันกับวิธีออกแบบ Width และ Length ของ M5 และ M9 และสุดท้ายเราจะได้วงจร Symmetrical OTA with Cascode Current Mirror ดังรูป

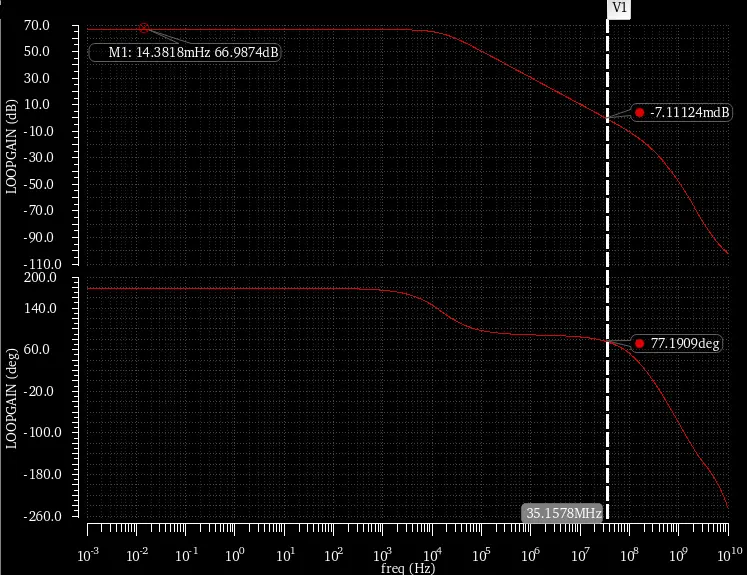

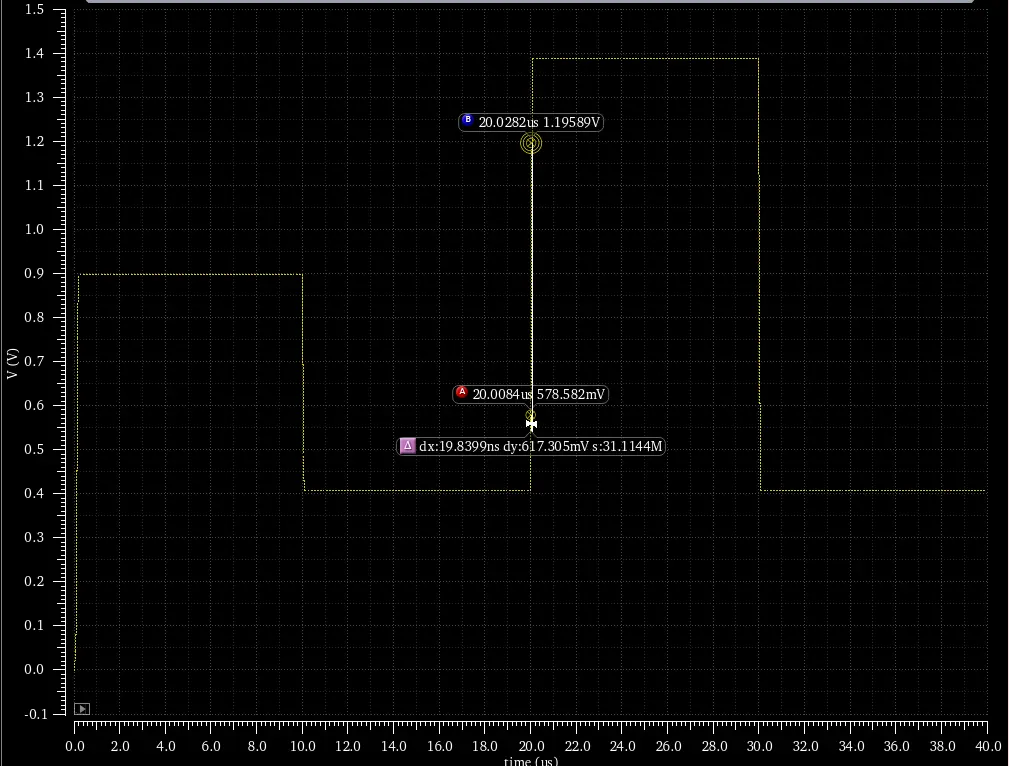

จากตัวอย่างที่ได้ออกแบบ เราทำการ Simulate วงจรและได้ผลลัพธ์ดังรูป

Open loop gain 67dB

UGBW 35MHz

Phase margin 77deg

Slew rate rise and fall อยู่ที่ประมาณ 24MV/s (อาจต้องเพิ่มกระแส หากต้องการ Optimize Slew rate)

ในบทความนี้เราได้ลองออกแบบ Opamp แบบ Single stage โดยใช้ Symmetrical OTA ร่วมกับ Cascode currrent mirror เพื่อให้ได้กำลังขยายที่สูงในระดับ 60dB และความเร็วระดับ 30MHz

ผม Kang T Lee ผมเขียนบทความเกี่ยวกับ Web development, IC Design, Business and Entrepreneur และเนื้อหาที่น่าสนใจจากหนังสือที่ผมอ่าน