หากใครเคยออกแบบออปแอมป์ (Opamp) หรือวงจรขยายอย่าง Common-Source Amplifier ที่ประกอบไปด้วยทรานซิสเตอร์ประเภท CMOS เราก็จะถูกสอนให้ใช้สมการที่มีความสัมพันธ์ระหว่างกระแส Id และแรงดัน Vgs เพื่อคำนวณหาค่าขนาด Width และ Length ของ Transistor ในแต่ละตัวออกมา อย่างไรก็ตาม ในบทความนี้เราจะมาเสนอวิธีใหม่ที่จะเป็นการทำ Characterization ตัว CMOS Transistor เพื่อให้เราได้ค่า Gm และ Rout เพื่อที่เราจะสามารถคำนวณหา Width และ Length ของทรานซิสเตอร์ออกมาในที่สุด ซึ่งการใช้วิธี Charactarization จะมีความแม่นยำและใช้เวลาน้อยกว่าการคำนวณด้วยตัวเองเป็นอย่างมาก

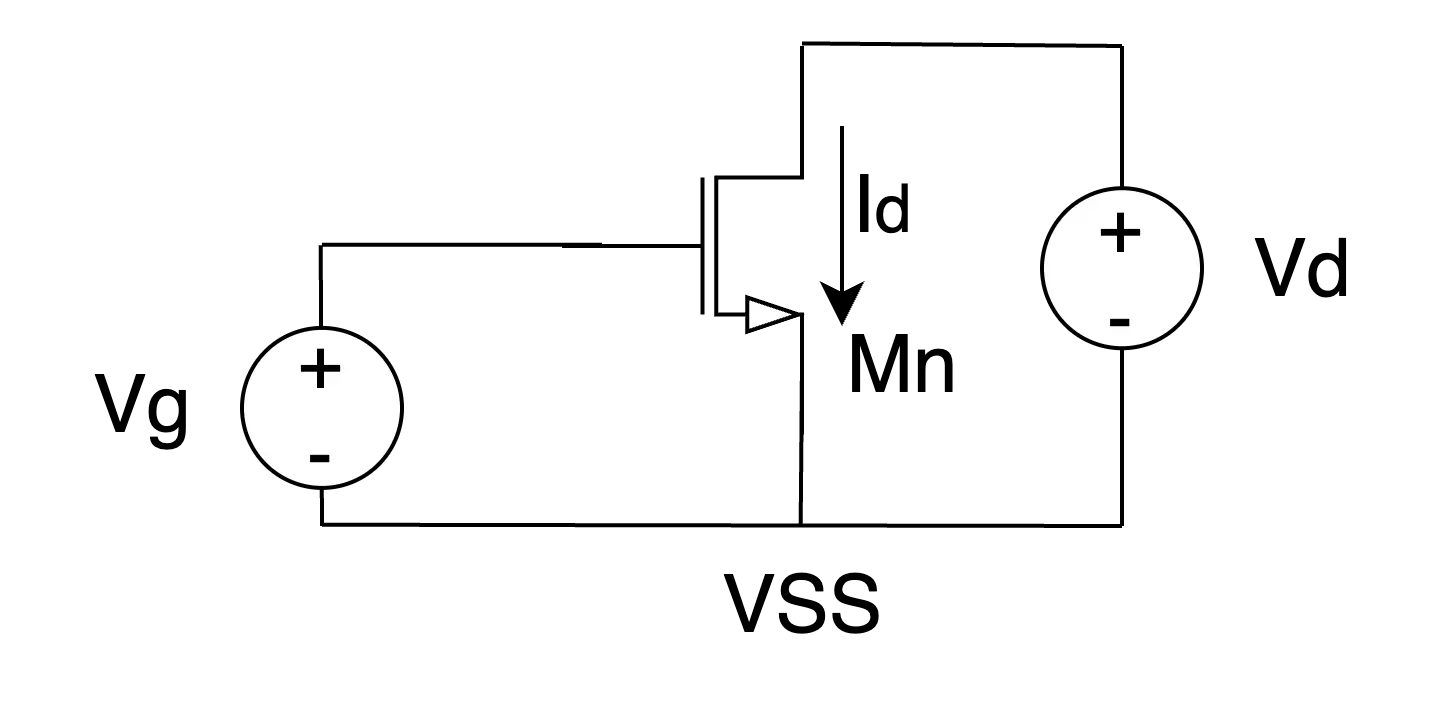

เรามาดูวิธีออกแบบขนาดของ CMOS Transistor เพื่อให้ได้ gm หรือ Rout ที่ต้องการกัน โดยเราจะใช้วงจร NMOS Transistor ข้างล่างนี้เป็น reference เพื่อพิจาณาวิธีออกแบบทรานซิสเตอร์

เมื่อเราป้อนแรงดันให้แก่ V_{gs} ของ CMOS Transistor Mn เพื่อให้ Mn อยู่ในสถานะ Saturation ด้วยเงื่อนไข V_{gs} \geq V_{dsat}+V_{th} เราจะได้กระแส Drain current I_d ที่จะเพิ่มขึ้นแบบยกกำลังสองของแรงดัน Gate-Source V_{gs}เป็น

I_d= \frac{W}{L} \frac{\mu C_{ox}}{2} \left( V_{gs}-V_{th} \right)^2 \left( 1+\lambda V_{ds} \right)

และหากเราต้องออกแบบ Transistor เพื่อใช้ออกแบบวงจรขยาย เช่น Opamp เราก็มักจะสนใจค่า Transconductance Gm ของ CMOS Transistor ซึ่งมีค่าเป็น

gm= \sqrt{2\mu C_{ox} \frac{W}{L}I_d}

จากสมการ ถ้าเราสามารถหาค่า \mu C_{ox} ออกมาได้ (ซึ่งเรามักจะหาได้จาก datasheet ของตัว Transistor) เราก็สามารถคำนวณหา Width และ Length ของทรานซิสเตอร์เพื่อให้ได้ gm ที่เราต้องการได้

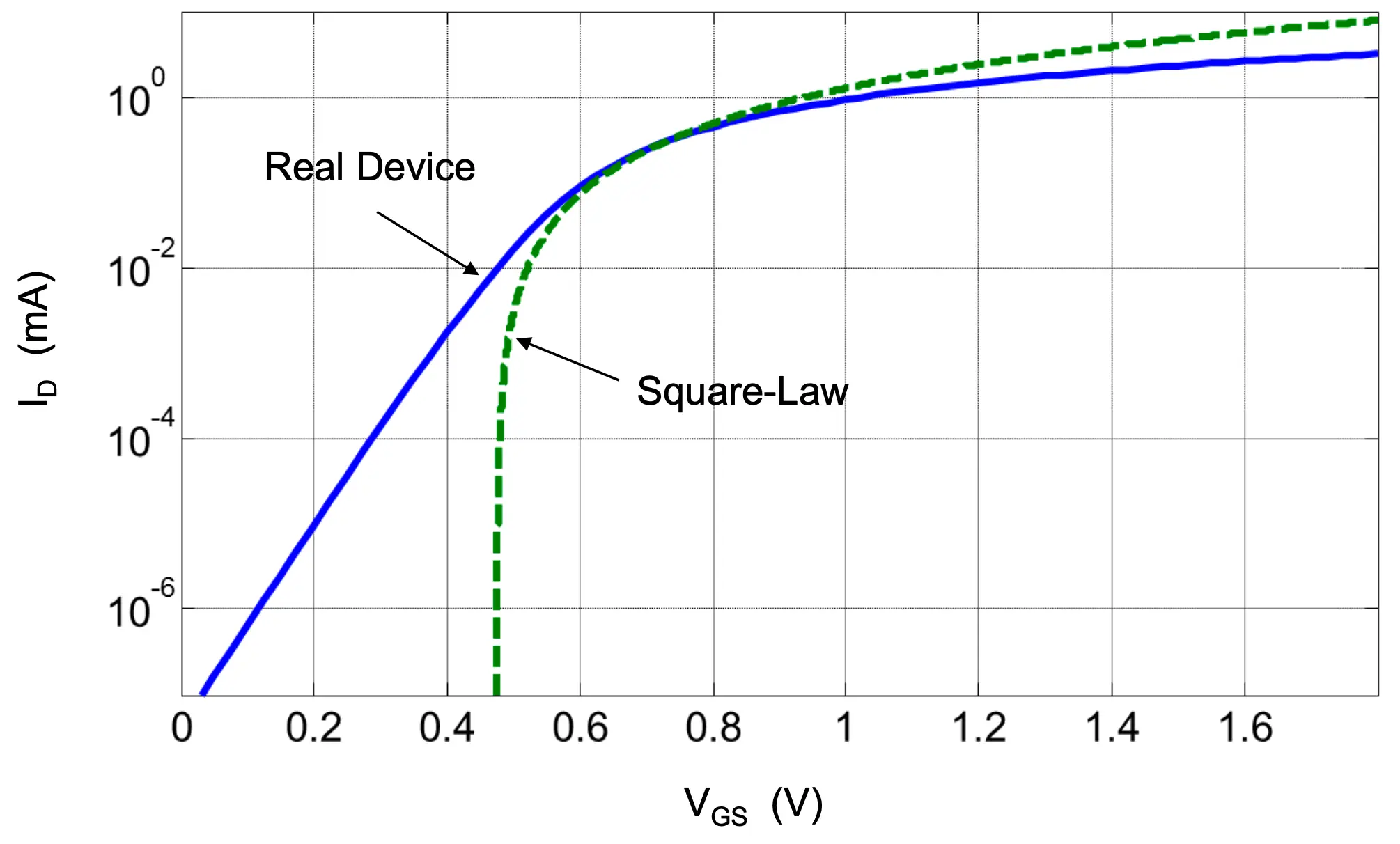

อย่างไรก็ตาม สมการดังกล่าวเป็นสมการที่เกิดขึ้นจากการประมาณการเท่านั้น หากเราทำการพลอตกราฟ Id vs Vgs โดยเทียบสมการ กับการทดลองจริง หรือ Simulate วงจร เราจะพบว่าสมการดังกล่าวจะมีความคลาดเคลื่อนจากผลลัพธ์จากการทดลองจริงเป็นอย่างมาก ดังนั้น หากเราลองออกแบบวงจรขยายแรงดัน เช่น Opamp หรือ Common-source amplifier เราก็มักจะได้ผลลัพธ์ที่ไม่ตรงกับการคำนวณ

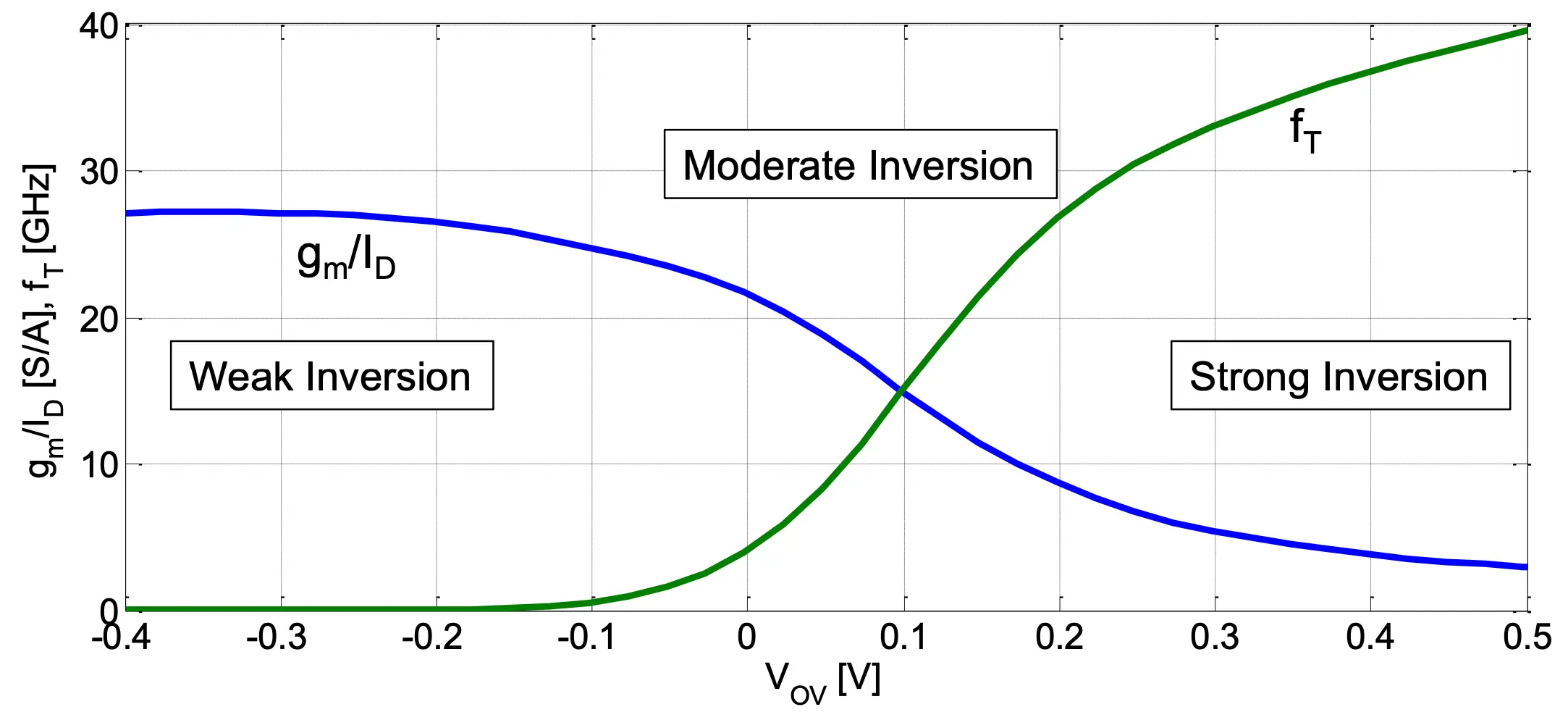

(ภาพจาก Systematic Design of Analog Circuits Using Pre-Computed Lookup Tables โดย Boris Murmann)

สมการ Id vs Vgs ถูกคิดค้นขึ้นเพื่อให้เราสามารถทำนายหาความสัมพันธ์ระหว่างกระแส Id กับ Vgs ของวงจร Transistor ได้ จุดประสงค์ของการคิดค้นสมการขึ้นมา คือเราต้องการรู้ว่าเมื่อเราป้อนแรงดัน 1V เราจะได้กระแสกี่ Amp ยิ่งสมการมีความแม่นยำเท่าไหร่ เราก็จะยิ่งสามารถทำนายค่ากระแสที่ได้จากการป้อนแรงดันออกมาได้อย่างแม่นยำขึ้นเท่านั้น แต่ถ้าเรามีกราฟที่พลอตจากการทดลองป้อนแรงดันและวัดกระแสออกมาอยู่แล้วหละ ? ดังเช่นกราฟข้างล่างนี้ หากเรามีกราฟที่เกิดจากการทดลองอยู่แล้ว เราก็สามารถทำนายค่าอของกระแสไฟฟ้าที่เกิดขึ้นจากการป้อนแรงดัน 1V ได้อย่างแม่นยำ เนื่องจากเราได้ทำการทดลองป้อนแรงดัน 1V และวัดกระแสไปแล้วนั่นเอง!! นี่ก็คือไอเดียหลักของการใช้ Lookup table เสนอโดย Boris Murmann เพื่อใช้ในการออกแบบ Transistor

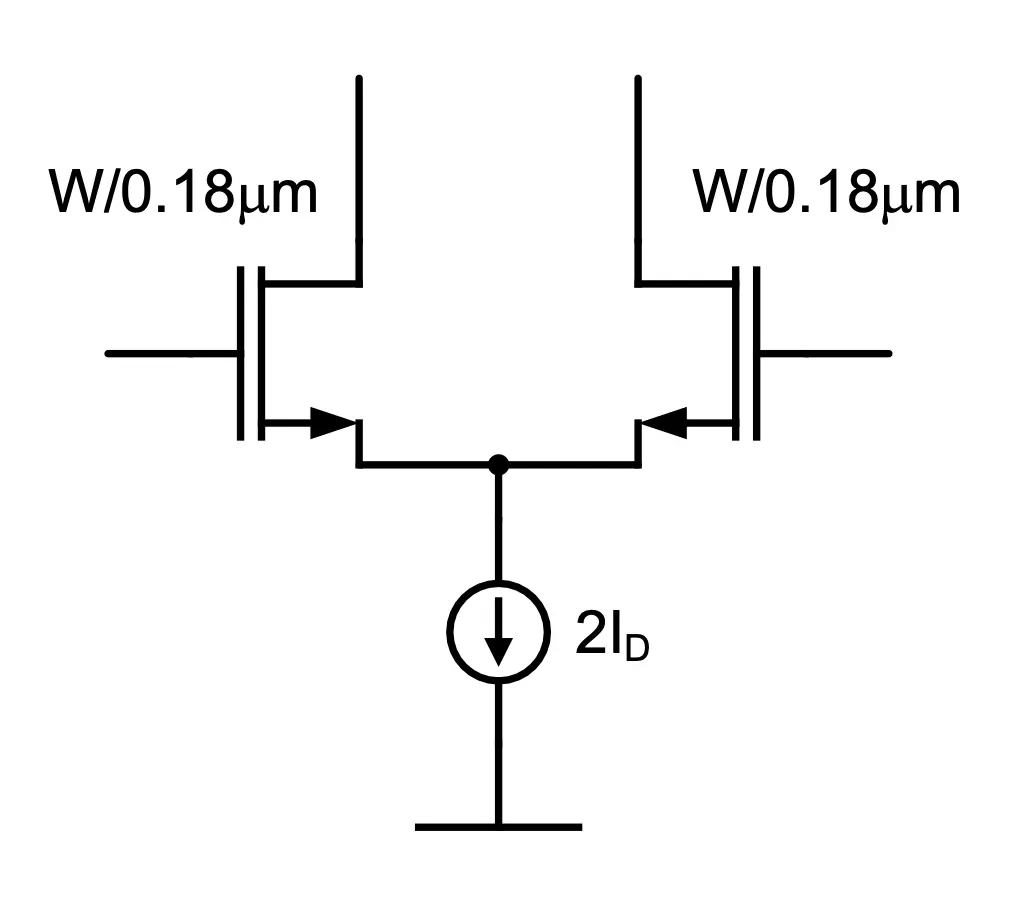

ก่อนจะอธิบายถึงขั้นตอนการทำ MOS Transistor Characterization ด้วยวิธีดู Lookup table เรามาดูตัวอย่างการใช้งานก่อน เพื่อให้เราได้เห็นภาพได้ชัดเจนมากขึ้น สมมติเราต้องการออกแบ NMOS Differential Pair ดังรูปข้างล่าง โดยเราต้องการให้ Gm มีค่าเท่ากับ 10mS จงหาค่า Width และกระแส Id ของ NMOS Transistor

เราจะเริ่มจากการเลือก Transistor ทำงานในสถานะ Moderate inversion โดยจะมี gm/Id = 15 (เราจะอธิบายเพิ่มถึงเหตุผลทีหลัง) ดังนั้นเราจะได้

I_d=0.67mA

เพื่อให้ง่าย เราจะเลือก L=0.18um (เลือกค่าอื่นได้ แต่เราจะอธิบายวิธีเลือก L ในภายหลัง)

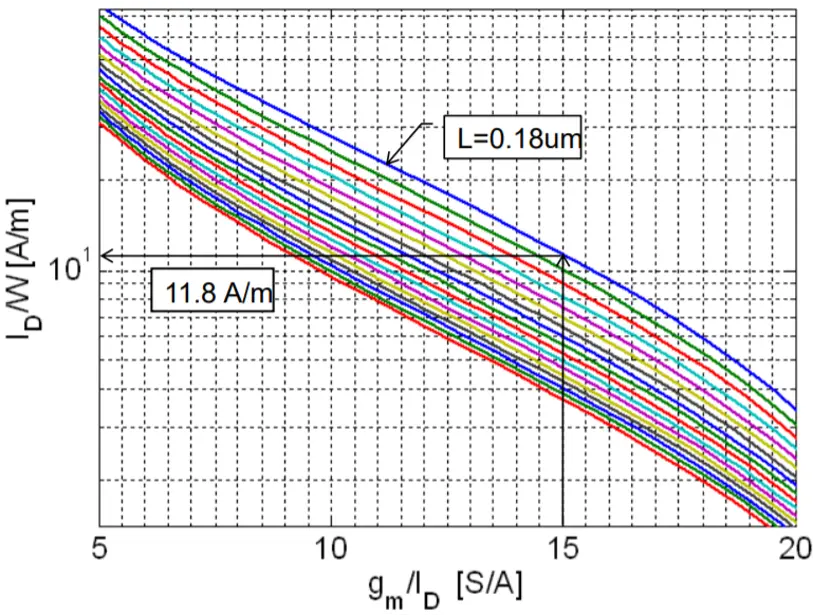

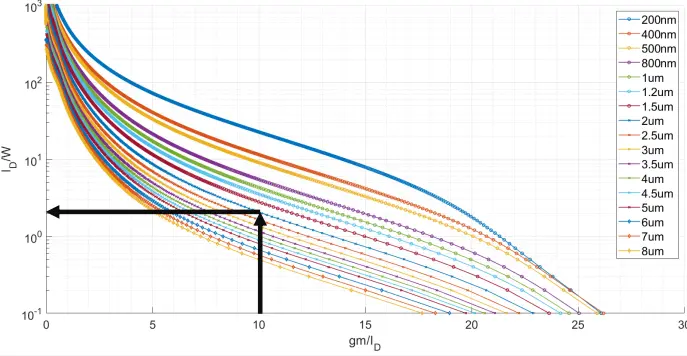

และเมื่อเราเทียบกราฟ Id/W vs gm/Id ที่ L=0.18um เราจะได้ Id/W = 11.8 และเราจะได้ W=56.6um ในที่สุด

จะเห็นไดเว่า หากเรามีกราฟที่เกิดจาการ Simulate อยู่แล้ว เราจะสามารถคำนวณหา Width ของ Transistor ตาม Gm ที่ต้องการได้อย่างรวดเร็ว

เราจะเริ่มจากการรู้จักกับตัวแปรสำคัญที่เราจะบ่งบอกถึงประสิทธิภาพ (หรือเราเรียกกันว่า Figure of Merit, FOM) ที่จะบอกว่า Transistor ที่ออกแบบนั้นมีประสิทธิภาพแค่ไหน โดยตัวแปร FOM ที่เราจะพิจารณาจะมีดังนี้

Transconductance Efficiency หรือ ประสิทธิภาพของ Gm จากสมการ

\frac{gm}{I_d}=\frac{2}{V_{ov}}

โดย Vov คือ overdrive voltage หรือ Vdsat นั่นเอง

Transconduction efficiency หรือ gm/id จะบ่งบอกว่า Transistor มีประสิทธิภาพที่จะผลิต Gm ได้ดีแค่ไหน ด้วยกระแสที่มี หากมีประสิทธิภาพสูงก็หมายความว่าเราสามารถออกแบบให้ Transistor มีค่า Gm ที่สูงด้วยกระแสเพียงน้อยนิดได้นั่นเอง

Transit Frequency หรือ ft=gm/Cgg จะบ่งบอกถึง Bandwidth ของตัว Transistor โดยจะขึ้นตรงกับ Cgg (Total gate capacitance ของ CMOS Transistor) ซึ่งจะมีความสำคัญสำหรับการออกแบบวงจรความถี่สูง หรือเมื่อเราต้องการพิจารณา non-dominant pole ในวงจรขยายที่มี Feedback loop เช่น 2-Stage Opamp โดยเราต้องการพิจารณา gm/Cgg ให้มีค่าที่สูงเพื่อที่เราจะได้ค่า Gm ที่สูงโดยไม่ต้องมีค่า Cgg ที่สูงตามไปด้วย

Intrinsic Gain หรือ gm/gds หรือ gm\cdot rds จะมีผลต่อกำลังขยายของ Transistor เมื่อเราต้องการออกแบบวงจรขยาย หรือ R_{out} ของ Transistor โดยเราต้องการ gm ที่สูงพร้อมกับ rds ที่สูงด้วยเช่นกัน

เราไม่สามารถออกแบบเพื่อให้ได้ตัวแปร FOM ที่สูงทั้งสามตัวแปรในคราวเดียวกันได้ หากเราต้องการ Transistor ที่มีค่า Gm ที่สูงโดยใช้กระแสที่ไม่มากนัก (gm/id สูง) นั่นหมายความว่าเราต้องออกแบบให้ Transistor มีขนาดความกว้าง Width ที่ใหญ่มากๆ เพื่อที่จะได้ค่า Gm ที่สูง และเมื่อเราออกแบบ Transistor ออกมาให้มีขนาดใหญ่ แน่นอนว่า Parasitic capacitor ที่ Gate หรือ Cgg ก็ต้องมีขนาดที่ใหญ่ด้วยเช่นกัน นั่นทำให้ ft ของ MOS Transistor มีประสิทธิภาพต่ำนั่นเอง และนี่คือ Design Tradeoff ของการออกแบบ Transistor โดยเราจะต้องเลือกออกแบบ Transistor ตามการใช้งาน เพื่อให้ได้ MOS Transistor ที่สามารถทำงานได้อย่างมีประสิทธิภาพตามที่เราต้องการ

กราฟที่แสดงอยู่ข้างล่าง จะเป็นกราฟความสัมพันธ์ระหว่าง Vov กับ gm/id และ Vov กับ ft ของ MOS Transistor โดยเราจะสามารถแบ่งช่วงออกมาเป็นสามช่วง ซึ่งจะเป็นช่วงสถานะการทำงานของ MOS Transistor โดยจะแบ่งเป็นช่วง

Weak Inversion

gm/id ประมาณ 25 ขึ้นไป

ใช้กระแสน้อย ก็ได้ Gm สูง

โดยส่วนใหญ่ Transistor ในช่วงนี้ จะอยู่ในสถาระ Subthreshold

Capacitor สูง (ft ต่ำ)

ไม่ค่อยได้ใช้ ยกเว้นในวงจรที่ต้องการกำลังไฟต่ำ เช่น nano-Watt หรือวงจรที่ต้องการ Gm คงที่ (ทำตัวคล้า BJT)

Strong Inversion

gm/id ต่ำกว่า 5

ใช้กระแสสูง

มีขนาด Transistor ที่เล็ก ซึ่งทำให้ Capacitor ต่ำตามไปด้วย (ft สูง)

เหมาะกับวงจรความถี่สูง และวงจร Current Mirror

Moderate Inversion

gm/id ช่วงประมาณ 10-20 (หรือ 5-25)

มีความสมดุลระหว่าง Gm/Id และ Ft

เหมาะกับวงจรกำลังขยาย

เราจะทำการ Simulate วงจรเพื่อทำการ Characterize Transistor เพื่อพล็อต 3 กราฟสำคัญที่ใช้สำหรับออกแบบ Transistor ด้วยวิธีดู Lookup table

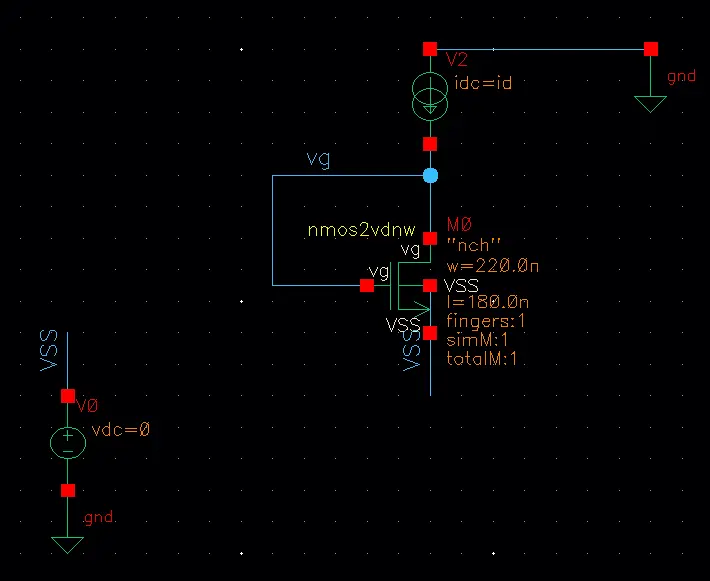

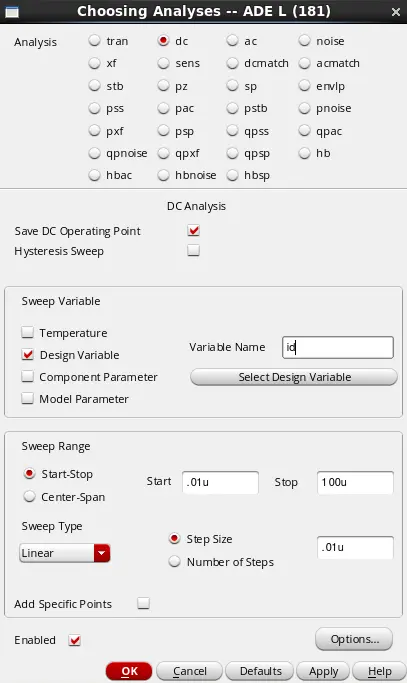

วงจรที่เราจะทดสอบคือวงจร Diode connected Transistor (เราใช้ NMOS ในตัวอย่างนี้ แต่เราสามารถทดสอบกับ PMOS ได้เช่นกัน) โดยเราจะ Run DC simulation ด้วยการ Sweep กระแส Id จากน้อยไปมาก นอกจากนี้เราก็จะทำการ Simulate ซ้ำด้วยการเปลี่ยนค่า L ตั้งแต่น้อยไปมากเช่นกัน

รูปตัวอย่างการ Run DC simulation ด้วยการป้อนกระแส id ที่จะ Sweep จาก 10nA เพิ่มไปถึง 100uA

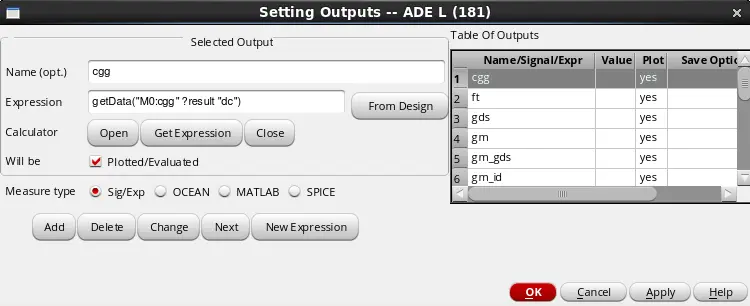

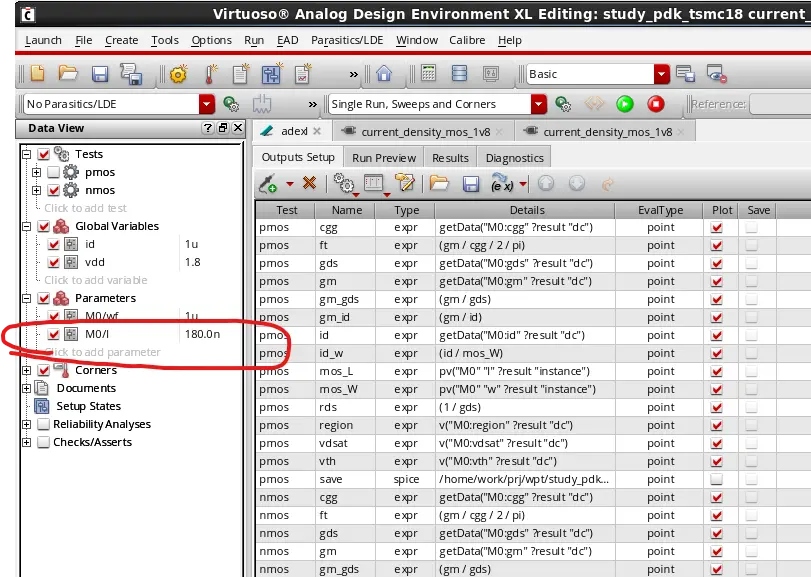

ใน ADE เราจะทำการ Setup Output ดังนี้:

name: gm Expression: getData("M0:gm" ?result "dc")

name: cgg Expression: getData("M0:cgg" ?result "dc")

name: gds Expression: getData("M0:gds" ?result "dc")

name: rds Expression: (1 / gds)

name: id Expression: getData("M0:id" ?result "dc")

name: vdsat Expression: v("M0:vdsat" ?result "dc")

name: vth Expression: v("M0:vth" ?result "dc")

name: gm_id Expression: (gm / id)

name: mos_l Expression: pv("M0" "l" ?result "instance")

name: mos_w Expression: pv("M0" "w" ?result "instance")

name: id_w Expression: (id / mos_w)

name: gm_gds Expression: (gm / gds)

name: ft Expression: (gm / cgg / 2 / pi)

name: region Expression: v("M0:region" ?result "dc")

นอกจากนี้ เรายังต้องสร้างไฟล์ชื่อ save.txt (ชื่ออะไรก็ได้) โดยในไฟล์จะเขียนว่า

save M0:gm

save M0:id

save M0:cgg

save M0:gds

save M0:vth

save M0:vdsat

save M0:l

save M0:w

save M0:region

จากนั้นเราจะทำการ save file ดังกล่าวด้วยการเลือก Measure type เป็น SPICE และกดเลือกไฟล์ save.txt ใน Script File ดังรูปข้างล่าง

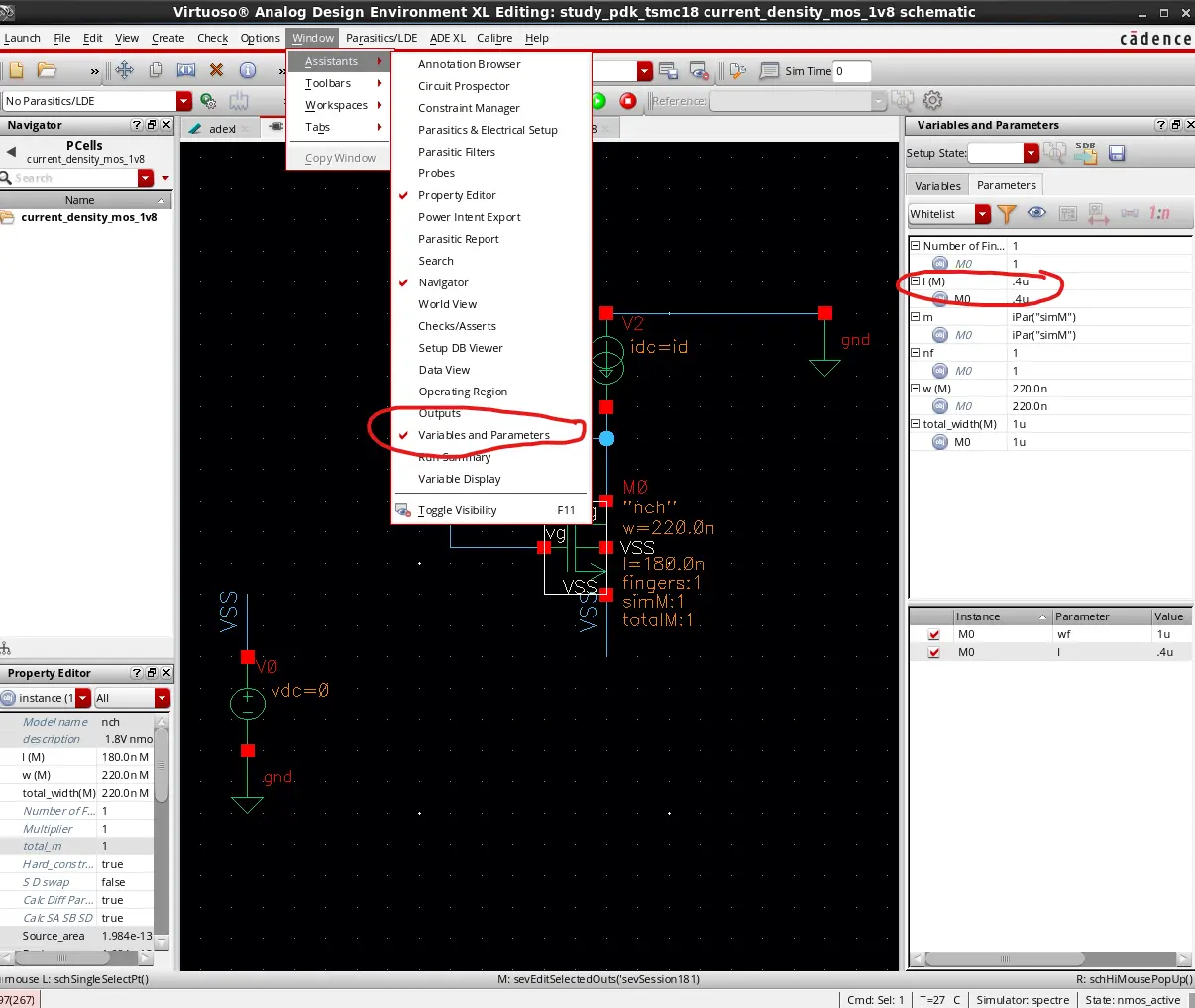

จากนั้นให้เราเปิด ADE XL เลือกเปิดหน้าวงจร และเลือก Window > Assitants > Variables and Parameters ตามรูป

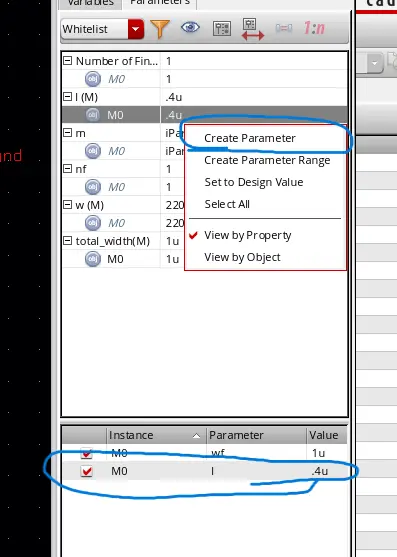

จากนั้นให้เราคลิ๊กเลือก Transistor M0 และตรงช่อง Variables and Parameters ที่ค่า Length ของทรานซิสเตอร์ ให้เราคลิ๊กขวา และเลือก Create Parameter

เมื่อกดเลือก Create Parameter เราก็ได้จะได้ตัวแปร l ปรากฎขึ้นมาในช่อง Parametersดังรูป เท่านี้เราก็จะสามารถทำการ Sweep อย่างเช่นกำหนดเป็น 200n:200n:4u ซึ่งจะหมายถึงการ Sweep จาก L=200nm ขึ้นไปเป็น 4um ด้วยความละเอียด 200nm นั่นเอง

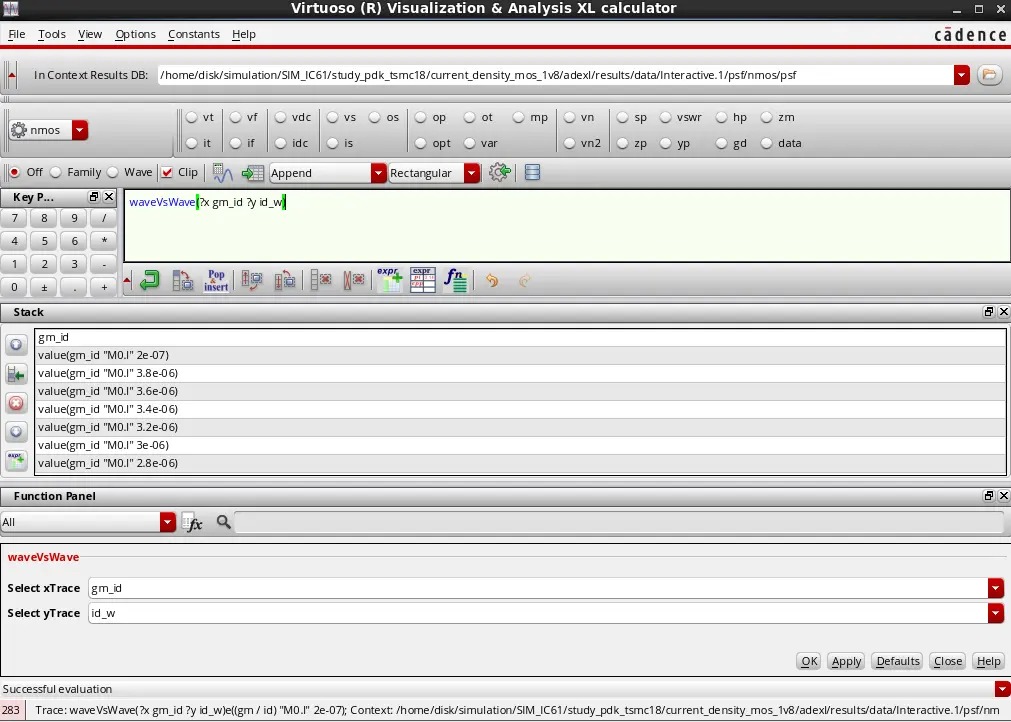

เมื่อเราได้ผลลัพธ์จากการทำ DC Simulate ด้วยการกวาดกระแสจาก 10nA ขึ้นไปถึง 100uA พร้อมกับการเพิ่ม L เป็น step ทีละ 200n เริ่มจาก 200n ขึ้นไปจนถึง 10um เราจะทำการพล็อตกราฟ Y vs Y จากผลลัพธ์ที่ได้โดยใช้ Calculator ดังรูป (มองหารูปเครื่องคิดเลขในหน้า ADE XL ตรงหน้า result)

โดยเราจะพล็อต 3 กราฟสำคัญดังนี้

Current Density: waveVsWave(?x gm_id ?y id_w)

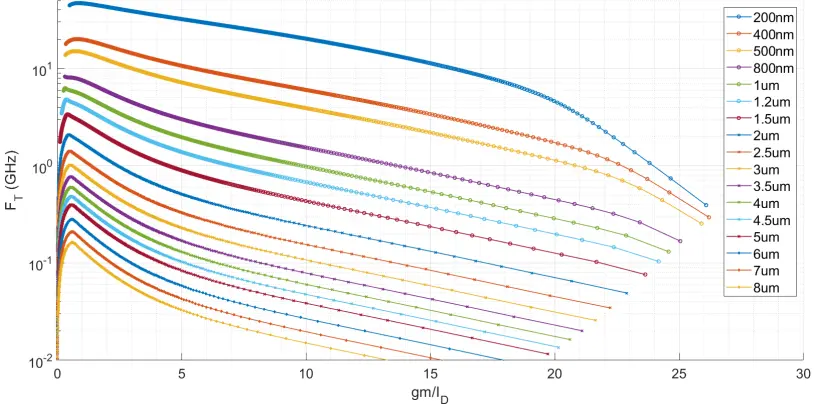

Transit Frequency: waveVsWave(?x gm_id ?y ft)

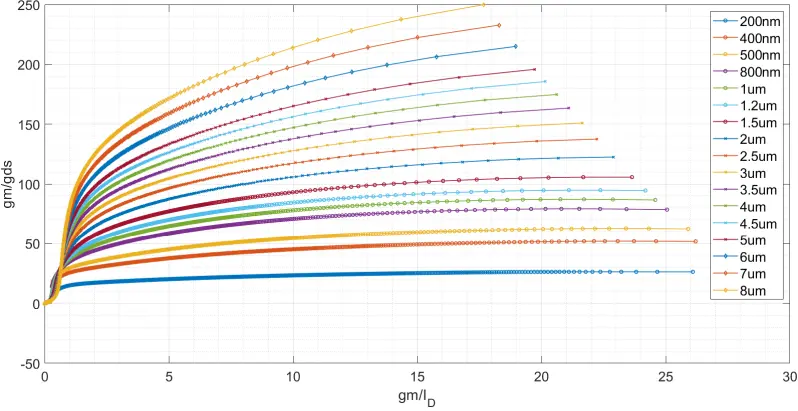

Intrinsic Gain: waveVsWave(?x gm_id ?y gm_gds)

เราจะได้กราฟที่ต้องการดังรูป (ในตัวอย่าง ผม Export เป็น Table และเซฟเป็น .csv ไฟล์ จากนั้นผมนำข้อมูลมาพล็อตบน Excel)

กราฟ Current Density แสดงผลระหว่าง Id/W กับ gm/Id

กราฟ Transit Frequency แสดงผลระหว่าง ft (gm/cgg) กับ gm/id

กราฟ Intrinsic Gain แสดงผลระหว่าง gm/gds กับ gm/id

เพียงเท่านี้ เราก็จะได้กราฟที่ใช้เป็น Lookup table สำหรับการเลือกค่า W และ L เพื่อให้ได้ Gm ของ Transistor ที่ต้องการ

สำหรับวิธีการออกแบบ Transistor โดยใช้ Lookup table จะมีขั้นตอนดังนี้

เลือก Gm (จาก Design Specification)

เลือก Length ของ Transistor

L สั้น หรือ short channel เราจะได้ Ft ที่สูง

L ยาว หรือ long channel เราจะได้ Intrinsic gain ที่สูง

หรือ เราสามารถเลือกโดยเริ่มจากการเทียบกราฟใน Intrinsic Gain ได้เลย (จะแสดงให้ดูในตัวอย่างภายหลัง)

เลือก gm/id หรือ Ft โดยพิจารณา

เลือก gm/id ที่สูง (moderate/weak inversion) สำหรับวงจรที่ต้องการประหยัดไฟ หรือวงจรที่ต้องการให้มี Large signal swing (Low distortion)

เลือก gm/id ที่ต่ำในกรณีที่ต้องการ Ft ที่สูง หรือต้องการให้มี pole อยู่ที่ความถี่สูง ๆ

คำนวณหากระแส Id จาก gm และ gm/id ที่เลือก

ใช้กราฟเพื่อค้นหา Id/W และทำการคำนวณหา W

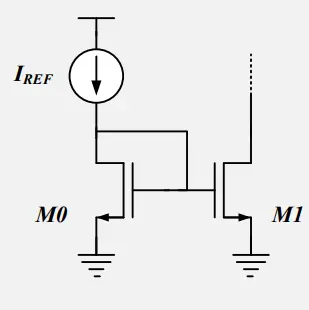

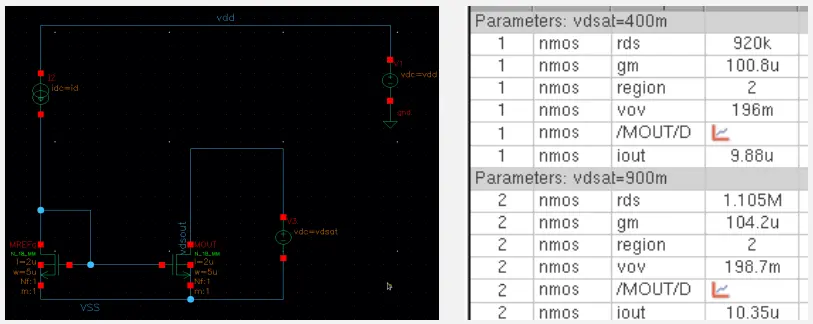

ต้องการออกแบบ NMOS current mirror เพื่อจ่ายกระแส 10uA โดยมี Iref = 10uA เช่นกัน โดยที่เราต้องการให้ Vdrain ของ M1 สามารถแกว่งลงต่ำสุดถึง 200mV (Vdsat=200mV) และ Output resistance ของ M1 เป็น 1M\Omega

เนื่องจากโจทย์ได้กำหนดเงื่อนไขของ Vov (หรือ Vdsat) ดังนั้นเราจึงสามารถคำนวณหา gm และ gm/id ได้เป็น

\frac{gm}{I_d} = \frac{2}{v_{ov}} =\frac{2}{200mV}= 10

gm=2\cdot \frac{10\mu A}{200mV}=100\mu S

จากนั้นเราจะหาค่า W และ L จากการใช้ Lookup table

เราเริ่มจากการคำนวณหา Intrinsic gain ที่ต้องการจาก

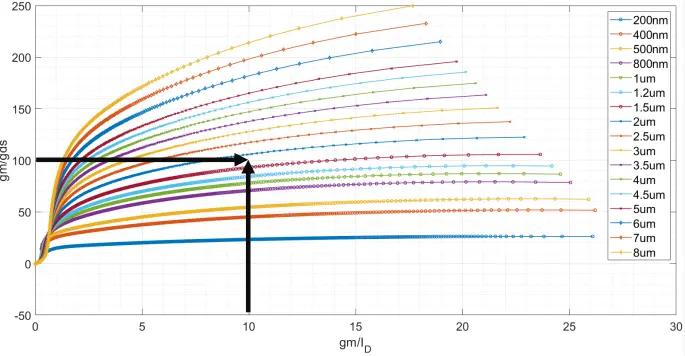

\frac{gm}{gds} = gm \cdot rds = 100uS \cdot 1M\Omega = 100

จากนั้น เมื่อเราเทียบกราฟ Intrinsic gain ที่ gm/id = 10 และ gm/gds=100 เราจะได้ L =2um นั่นเอง (ตามรูปข้างล่าง)

เมื่อเราได้ L แล้ว เราจะหาค่า W จากกราฟ Current density ที่ gm/id=10 และ L=2um เราจะได้ Id/W =2 ดังนั้นเราจะได้

W=\frac{I_d} { Id/W } =10\mu /2=5\mu m

หลังจากนั้น เราจะทำการทดสอบวงจรด้วยการทำ DC simulation ด้วยการป้อนกระแสและแรงดันให้แก่วงจร NMOS Current Mirror ตามรูปข้างล่าง

จากผลลัพธ์ที่ได้ดังรูป จะได้ Rout อยู่ที่ใกล้เคียงกับ 1M\Omega ตามที่ต้องการ!!

ในส่วนของการออกแบบวงจรขยาย เราสามารถใช้ตัวอย่างคล้ายกับตัวอย่างที่เคยแสดงให้เห็นในช่วงต้นของบทความได้ โดยเราสามารถใช้วิธีเลือก L จาก intrinsic gain หากเรารู้ว่าเราต้องการ Rout เท่าใด หรือเราจะเริ่มต้นเลือก L จากเงื่อนไขของความต้องการด้านความเร็ว (ft สูง) หรือความต้องการด้านการประหยัดพลังงาน (gm/id สูง) หรือเราจะเลือกแบบสมดุล (gm/id อยู่ที่ประมาณ 10-15)

นอกจากนี้ เราสามารถนำหลักการ MOS Characterization ที่อาศัยผลลัพธ์จากการ Simulate วงจรจริงมาประยุกต์เพื่อออกแบบวงจร เหมือนที่ผมได้แสดงดูในตัวอย่างการออกแบบ 2 Stage CMOS Opamp

ในบทความนี้เราได้ศึกษาเกี่ยวกับวิธีการออกแบบขนาด Width และ Length ของ Transistor เพื่อให้ได้ Gm หรือ Rout ตามที่ต้องการด้วยวิธีการหาค่าตัวแปรจาก Lookup table ที่เสนอโดย Boris Murmann แทนการคำนวณด้วยสมการที่เราเรียนรู้กันมาจากตำรา การใช้ Lookup table ในการคำนวณหาขนาดของ Transistor จะทำให้เราได้ค่า Gm และ Rout ที่ต้องการได้อย่างแม่นยำ เนื่องจาก Lookup table คือผลที่อ้างอิงจากการทดสอบวงจรด้วยการทำ DC simulation ในขณะที่การคำนวณจากสมการเป็นเพียงการสมมติค่าสมการ ทำให้ขาดความแม่นยำ และเกิดการคลาดเคลื่อนเมื่อเราเปรียบเทียบผลลัพธ์

หลักการ MOS Characterization เป็นหลักการที่สำคัญมากในการออกแบบวงจร และผมใช้เทคนิคนี้ทุกครั้งในการออกแบบวงจรเนื่องจากผลลัพธ์ที่ออกมามีความแม่นยำ หากใครสนใจที่จะอ่านเพิ่มเกี่ยวกับหลักการของ Lookup table ก็สามารถตามอ่านได้ที่ Systematic Design of Analog CMOS Circuits

ผม Kang T Lee ผมเขียนบทความเกี่ยวกับ Web development, IC Design, Business and Entrepreneur และเนื้อหาที่น่าสนใจจากหนังสือที่ผมอ่าน