บทความนี้จะสอนวิธีออกแบบ CMOS ออปแอมป์ (Operational Amplifier) หรือ CMOS Opamp โดยจะถูกแบ่งออกมาเป็นหลายตอน เราจะเริ่มจากการคำนวณโดยใช้ small signal model และจะเริ่มต่อยอดไปจนถึงการออกแบบ CMOS opamp ในทางปฏิบัติ

โดยปกติแล้ว ผมมักจะอธิบายที่มาที่ไปของหัวข้อที่ผมต้องการพูดถึง แต่ในบทความนี้ผมอยากจะเขียนเพื่อให้ผู้อ่านที่มีความรู้อยู่แล้ว และต้องการออกแบบ Opamp สามารถใช้บทความนี้เป็น reference ในการช่วยออกแบบ ผมจึงขอลัดขั้นตอนการอธิบาย และเข้าสู่วิธีการออกแบบเลย

ก่อนที่เราจะเริ่มออกแบบ CMOS Opamp สิ่งหนึ่งที่สำคัญคือเราต้องมีความรู้พื้นฐานของ MOS transistor และ small signal model ของ NMOS และ PMOS โดยบทความนี้จะไม่อธิบายเกี่ยวกับที่มาที่ไปของตัว small signal model และสมการที่เกี่ยวข้อง แต่จะเป็นการยกสมการขึ้นมาเลย

สมการและหัวข้อพื้นฐานที่คุณควรรู้

Gm ของ NMOS / PMOS

Rds ของ NMOS / PMOS

Small signam model ของ NMOS และ PMOS

นอกจากนี้ ผมยังจะใช้เทคนิคการ Characterize transistor ด้วยวิธีที่คล้ายกับการดู Lookup table ที่เสนอโดย Borrin Murmann ซึ่งผมอาจจะอธิบายถึงหลักการในบทความหน้าในอนาคต

หากใครที่ได้ผ่านการเรียนวิชาออกแบบ Analog IC ก็ต้องเคยเจอการบ้านให้ออกแบบออปแอมป์ 2 Stage ซึ่งเป็นวงจรพื้นฐานที่จะต้องใช้ความรู้เกือบทุกอย่างเกี่ยวกับ Analog Design เพื่อออกแบบวงจรออปแอมป์ 2 Stage นอกจากนี้ ทุกคนก็คงจะเคยคำนวณสมการเพื่อให้ได้ผลลัพธ์ที่ต้องการ และหากเราลองค้นหาวิธีออกแบบออปแอมป์จากตำราต่างๆ ก็มักจะพบว่าการออกแบบออปแอมป์จะเริ่มจากการมี Design Specification และทำการคำนวณหา Width และ Length ของทรานซิสเตอร์ทุกตัว และขั้นตอนสุดท้ายก็จะเป็นการ Simulate วงจรเพื่อวัดผลลัพธ์

แต่นั่นไม่ใช่วิธีที่ผมใช้ เวลาผมออกแบบ แน่นอนว่าผมเริ่มจากการใช้ Design Specification เพื่อออกแบบให้ได้ค่า Gm ที่ต้องการ แต่ผมมักจะทำการออกแบบโดยการแบ่งออปแอมป์และตัวทรานซิสเตอร์ออกเป็นทีละส่วน และทำการออกแบบแยกกัน โดยจะคอย Simulate ควบคู่ไปด้วย และทำการอัพเดทตัวแปร Gm และ Rout เพื่อให้ได้ผลลัพธ์ที่ต้องการ หากจะสรุปง่ายๆ หลักการของผมคือการ ออกแบบเบื้องต้น → Simulate → Iterate (ปรับปรุง หรืออัพเดท) ซึ่งผมพบว่าวิธีดังกล่าว ให้ผลลัพธ์ได้เร็วกว่าการออกแบบโดยการคำนวณด้วยสมการทั้งหมดตั้งแต่ต้น

โดยส่วนใหญ่ ในทางปฏิบัติ Specification ของ Opamp จะถูกกำหนดโดยการใช้งานของตัว Opamp เอง ยกตัวอย่างเช่น การออกแบบ Opamp เพื่อใช้เป็น ตัวขยายสัญญาณ Voltage Input ก่อนจะต่อเข้ากับตัว ADC เมื่อเรารู้ว่าตัว ADC (1) มี Input Capacitor อยู่ที่ขนาดเท่าไหร่ (2) มีความเร็วในการ Sampling อยู่ที่เท่าไหร่ เราก็จะสามารถคำนวณหา Spec. ของ Opamp ได้ โดยในบทความนี้ เราจะสมมติ Spec. ของออปแอมป์ขึ้นมา และในอนาคตผมจะสอนวิธีการแปลง Application Specification เพื่อให้ได้ Opamp Specification

Specification ของ Opamp ที่เราควรรู้มีดังนี้

Supply voltage

Loading Capacitor C_{Load}

Unity Gain Bandwidth, UGBW

DC Open Loop Gain, A_v

Input voltage range

Output voltage range

Slew rate

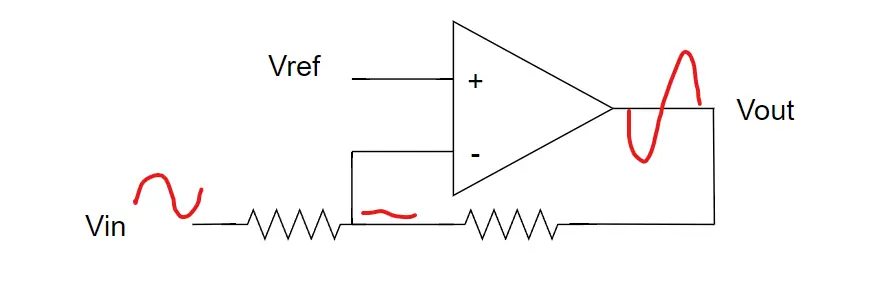

Input voltage range จะขึ้นกับลักษณะการใช้งานของ Opamp ด้วย เช่นหากเราใช้ Opamp เพื่อขยายสัญญาณในรูปแบบของ Inverting Amplifier เราจะไม่มีความจำเป็นต้องกังวลถึง Input voltage range เนื่องจากเรารู้ว่า Opamp Input จะมี Voltage อยู่ที่ประมาณ V_{ref} เสมอ แต่หากเราใช้ Opamp เป็น Voltage follower หรือ Non-inverting Amplifier เราจะต้องคำนึงถึง Input Voltage Range

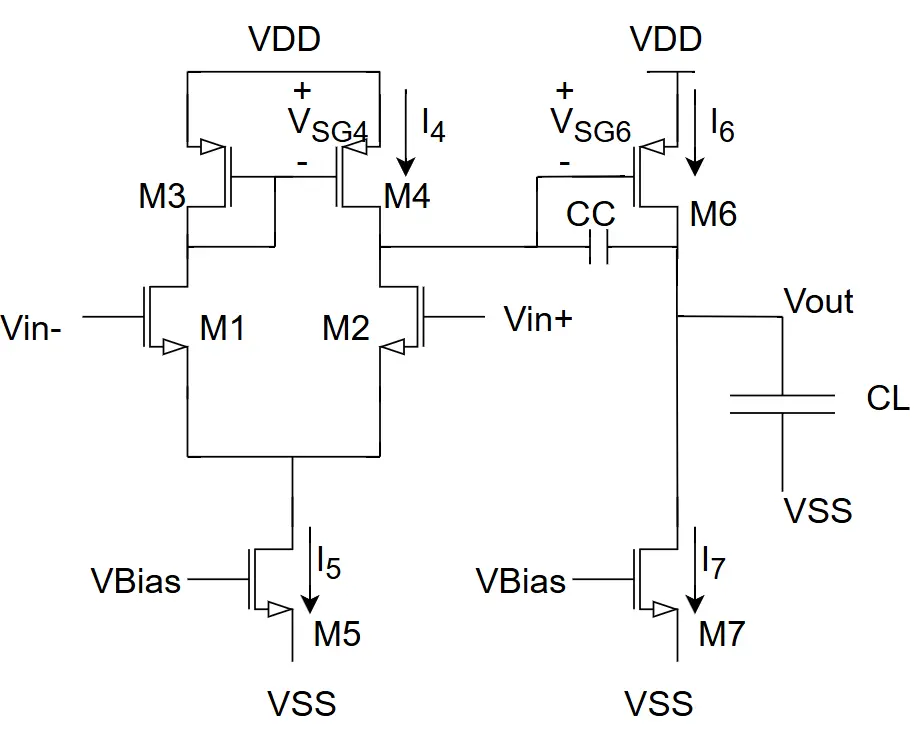

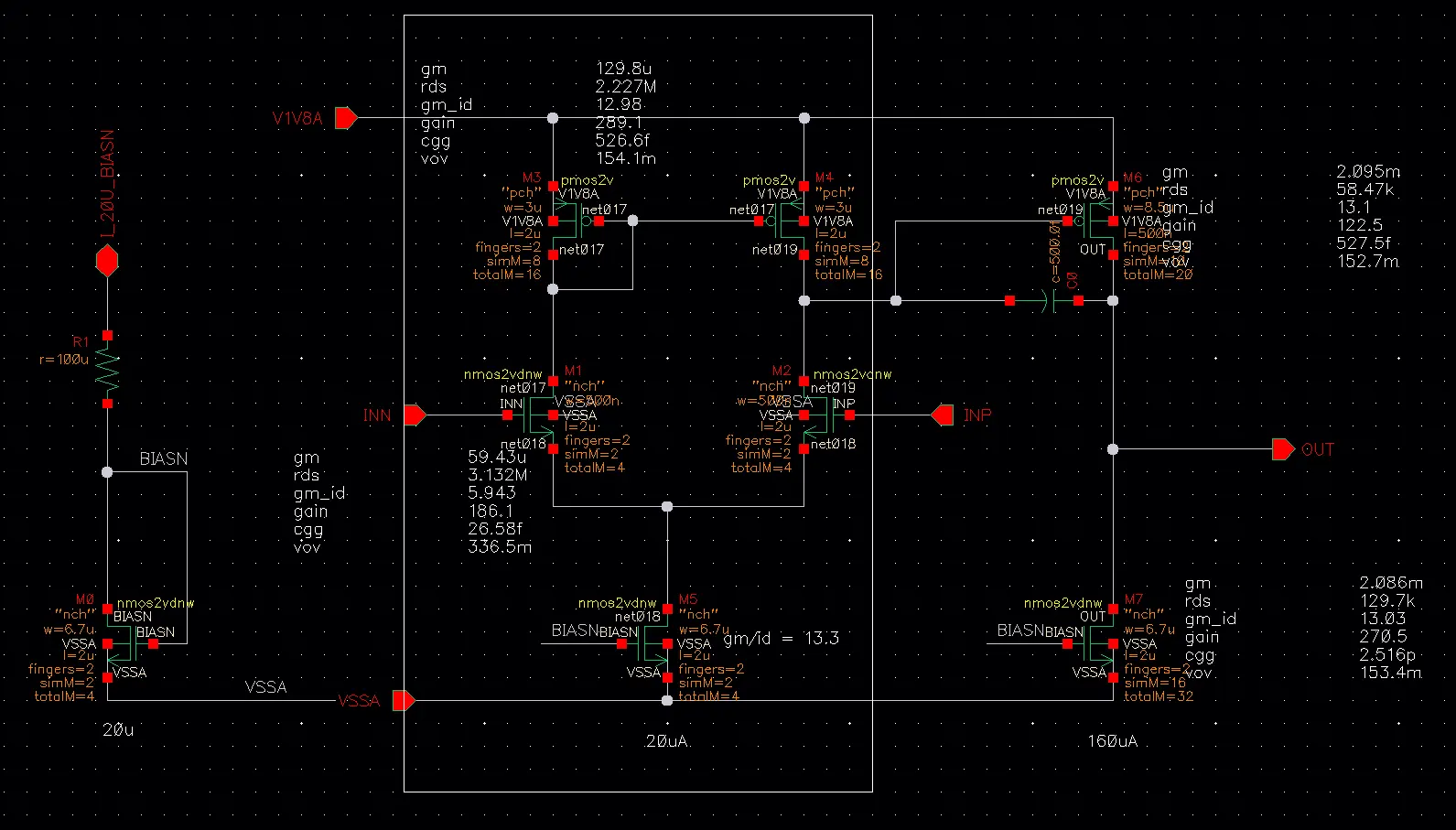

ผมจะแสดงตัวอย่างการออกแบบสำหรับ NMOS input pair เพื่อออกแบบ Single Ended Two Stage Opamp ตามรูปข้างล่าง โดยหลักการออกแบบของ PMOS input pair และ NMOS input pair จะไม่ต่างกันเลย คุณสามารถเปลี่ยนมาใช้ PMOS input pair โดยใช้หลักการออกแบบเหมือนกับที่ผมกำลังจะเสนอ

เราจะออกแบบตาม Design Specification ตัวอย่าง เพื่อให้เห็นภาพและเข้าใจได้ง่ายขึ้น อย่างไรก็ตาม คุณสามารถปรับเปลี่ยน Specification ได้ตามต้องการ โดย Design Specification ของเราจะมีดังนี้

Supply Voltage (VDD): 1.8V

Loading Capacitor: 1pF

Output voltage Min/Max: 0.2V - 1.6V

Open Loop Gain (Av): 80dB

UGBW: 10MHz

Slew Rate (SR): 30MV/s

เริ่มการออกแบบ...

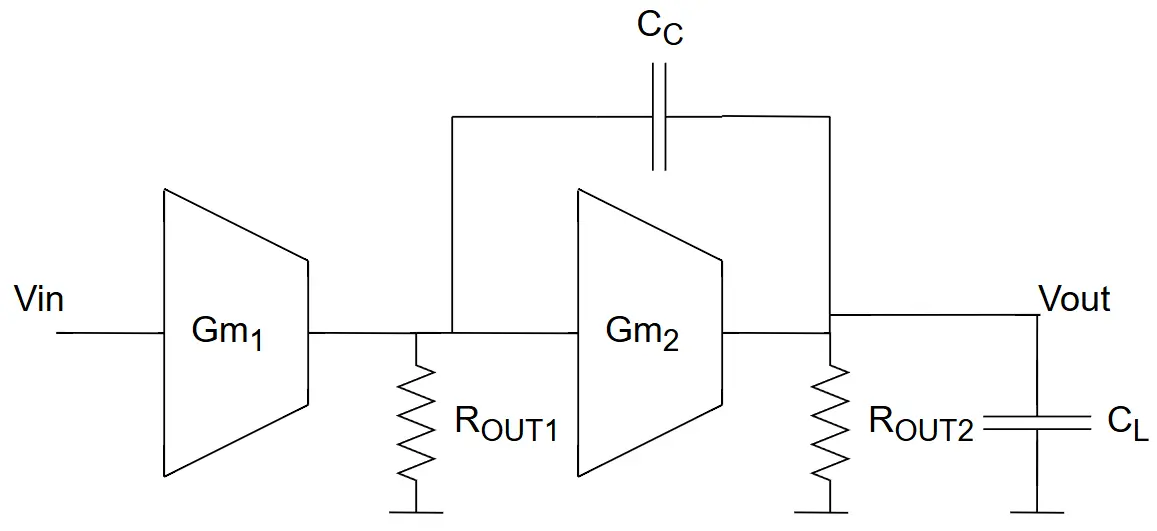

2.1.) เลือก Miller Capacitor C_C

เราจะเริ่มจากการเลือกค่า C_C จากสมการ

gm_2 \cdot C_C \approx 4\cdot gm_1 \cdot C_L

(สมการนี้ คำนวนจากการกำหนดให้ 2nd pole มีค่าเป็น 3 เท่าของ UGBW ซึ่งจะทำให้เราได้ Phase Margin อยู่ที่ประมาณ 70° ลองไปพิสูจณ์สมการกันดูนะครับ)

โดยจะเห็นว่าเรามีอิสระในการออกแบบตัวแปร C_C, gm_2 และ gm_6 เพื่อความง่าย เราจะเริ่มต้นด้วยการเลือก

C_C=0.5\cdot C_L หรือ C_C = 500fF นั่นเอง

2.2.) เลือก gm_2

จากสมการ

UGBW = gm_2\cdot\frac{2\pi}{C_C}

เราจะได้ gm_2=31.4\mu S

2.3.) เลือก I_5

การเลือกกระแส I_5 จะส่งผลถึงค่า Slew Rate จาก

SR = \frac{I_5}{C_C}

ซึ่งเราจะได้ I_5 = 18.8\mu A และเราจะเลือก I_5 = 20\mu A (เพิ่ม Margin เผื่อไว้)

2.4.) เลือก gm_4

การเลือก gm_4 ของวงจร Single Ended 2 Stage Opamp จะถูกจำกัดด้วย V_{dsat} (หรือ V_{ov}) นั่นคือ V_{dsat4}=V_{dsat6} เพื่อกำจัด Systematic Offset Voltage และเนื่องจาก Output Swing สูงสุดจะต้องสามารถแกร่งขึ้นไปสูงถึง 1.6V นั่นหมายความว่าเราจะต้องออกแบบ V_{dsat6} ให้มีค่าเท่ากับหรือน้อยกว่า 200mV นั่นเอง

ดังนั้น เราจะเลือก V_{dsat4} จาก \frac{gm}{I_d} = \frac2{V_{dsat}} เราจะได้ \frac{gm}{I_d} = 13.33 โดยค่า g_m/I_d ดังกล่าว จะทำให้เราได้ V_{ov} อยู่ที่ประมาณ 150mV

2.5.) เลือกกระแส I_7

สำหรับ Single Ended 2 Stage Opamp เราต้องออกแบบให้ I_5 \gg I_7 เพื่อให้ Slew Rate Rise มีค่าใกล้เคียงกับ Slew Rate Fall ดังนั้นเราจะเลือก I_7 = 5\cdot I_5 เราจะได้ I_7=160\mu A

เมื่อเราเลือกกระแส I_7 เราก็จะสามารถคำนวณหา gm_6 ได้เช่นกัน เนื่องจากเราได้กำหนดค่า V_{dsat6}=V_{dsat4} ดังนั้นเราจะได้ gm_6=2.13mS

2.6.) ออกแบบ Transistor สำหรับ Stage แรก ของ Opamp

ถึงจุดนี้ เราเหลือเพียงการกำหนดค่า R_{OUT1} และ R_{OUT2} เพื่อให้ได้ DC gain ที่ต้องการ ซึ่งสามารถทำได้โดยใช้วิธีของ Borrin Murmann ในการดูตาราง Lookup table อย่างไรก็ตาม การใช้ Lookup table อาจจะยุ่งยากสักนิดสำหรับคนที่ไม่มีโปรแกรมที่ช่วยคำนวณค่าออกมาอย่างรวดเร็ว ดังนั้น ผมจึงเสนอให้ลองเลือกค่า Rout จากการเลือกค่า L แล้วทดลอง Simulate ดูก่อน แล้วจึงแก้ไขหากค่าที่ได้ไม่ตรงตามความต้องการ

โดยเราสามารถคำนวณค่า R_{OUT1} \times R_{OUT2}ได้จาก

A_V=Gm_1 \cdot R_{OUT1} \cdot Gm_2 \cdot R_{OUT2} = gm_2 \cdot gm_6 \cdot R_{OUT1} \cdot R_{OUT2}

R_{OUT1}\cdot R_{OUT2}=1.5^{11} \Omega

เราจะเลือก R_{OUT1} ให้อยู่ที่ในช่วย M\Omega โดยเลือกเป็น \sim 1M\Omega เราจะได้ R_{OUT2}=150k\Omega

เหตุผลที่เราเลือก R_{OUT1} ให้มีค่าที่ใหญ่กว่า R_{OUT2} เนื่องจาก เมื่อเราสังเกตกระแสที่ไหลใน Transistor M4 เทียบกับกระแสที่ไหลใน Transistor M6 เราจะเห็นว่าการออกแบบ M4 ให้มีความต้านทาน R_{ds} ที่มาก จะทำได้ง่ายกว่า M6 เนื่องจาก R_{out} แปรผกผันกับกระแส I_d นั่นเอง ดังนั้นเราจะสามารถเลือกขนาดของ L4 ที่ไม่ต้องใหญ่เกินไปเพื่อให้ได้ R_{out}หลัก M\Omega(แต่เราต้องเลือกขนาด L6 ที่ใหญ่กว่ามาก หากต้องการ R_{out}ขนาดใหญ่)

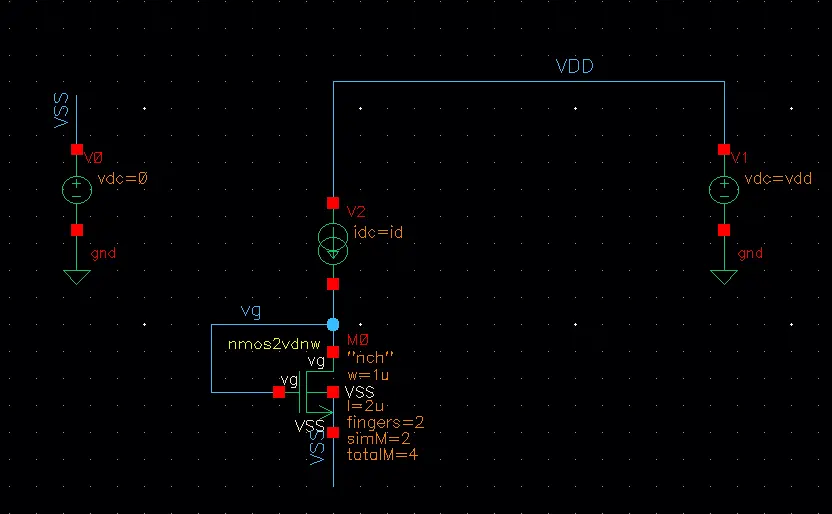

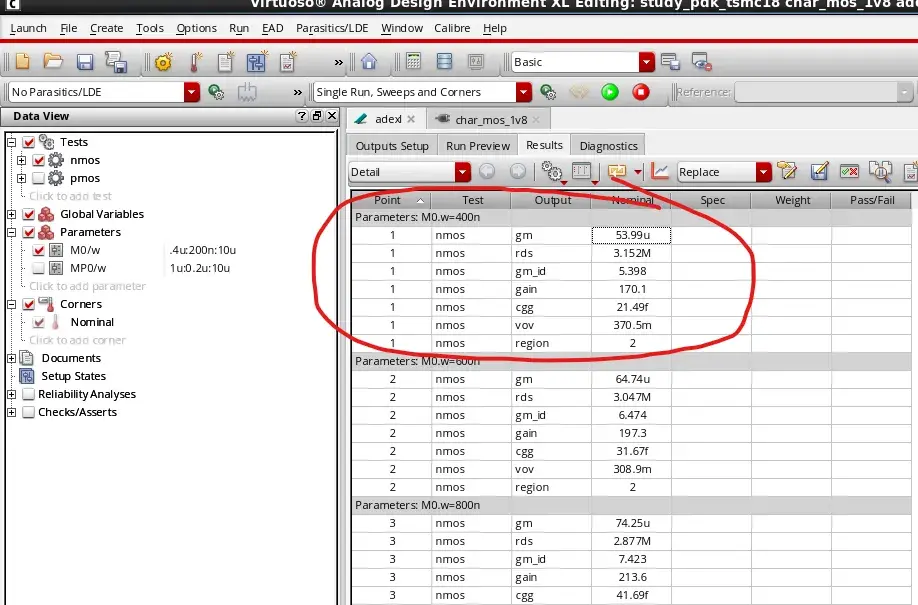

ทำการ Simulate วงจร Diode connected NMOS และ PMOS ตามรูป โดยกำหนดกระแสให้เป็น 10uA และเลือกค่าเริ่มต้นของ W และ L โดยเราจะเลือก L ให้อยู่ที่ 2um (เลือกค่าอะไรก็ได้ เพียงลองเลือกและ Simulate เพื่อวัดผล Rds ที่ได้) (ส่วนค่า W ยังไม่สำคัญมากนัก เลือกตัวเลขที่ใกล้เคียง L ก็ได้)

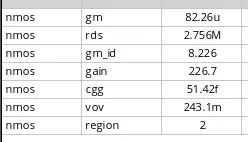

จากการเลือก L=2um เราจะได้ Rout ออกมาประมาณ 2.76Mohm (หากค่า Rds ที่ได้มีค่าต่ำเกินไป เราจะลองเพิ่มค่า L แล้ว Simulate จนกว่าจะได้ค่า Rds ที่ต้องการ การใช้วิธีนี้จะเร็วมากเพราะวงจรมีขนาดเล็ก)

เมื่อได้ค่า L ของ Transistor M2 ที่ต้องการแล้ว เราจะ Sweep W (เพิ่มทีละ 200nm จาก 400nm ไปจนถึง 10um) เพื่อหา gm ที่ต้องการ

สุดท้ายเราจะได้ L2=2um และ W2=400nm (และ finger=2, multiplier=2 ทำให้ total width เป็น 1.6um)

และจาก W,L ของ Transistor M2 เราก็จะได้ gm2=59.43uS และ rds2=3.13MOhm

และในส่วนของ Transistor M4 เราจะใช้วิธีเดียวกัน โดยเราเริ่มต้นด้วย L4=2um (1) หาค่า Rout ให้ใกล้เคียง 2-3MOhm และ (2) ทำการ Sweep W เพื่อให้ได้ gm/id อยู่ที่ประมาณ 13.33 ซึ่งจะทำให้เราได้ rds4=2.23MOhm

เมื่อเราได้ค่า W,L ของ M2 และ M4 แล้ว เราก็จะสามารถคำนวณหา Gain และ Rout ของ Stage แรกได้เป็น

R_{OUT1} = r_{o2} \parallel r_{o4} = 1.3M\Omega

Gm_1 = 59.4\mu S

A_{V1} = Gm_1\cdot R_{OUT1} = 77.4 V/V

2.7.) ออกแบบ Transistor ของ Opamp Stage ที่สอง

เราจะเหลือ A_{V2} ที่ต้องออกแบบเพื่อให้ A_V = A_{V1}\cdot A_{V2} = 10^4 เป็น A_{V2}=129 V/V โดยเราไม่สามารถเลือก gm_6 เองได้ เนื่องจากค่า gm_6จะถูกกำหนดโดย V_{dsat4} และกระแส I_7 ที่เราได้เลือกมาก่อนหน้านี่แล้ว ดังนั้นเราจะได้ Gm_2 = gm_6 = (gm/I_d) \cdot I_7 = 2.13mS

และสุดท้าย เราจะได้ R_{OUT2}ที่จะต้องมีค่าอย่างน้อย R_{OUT2}\gt \frac{A_{V2}}{gm_2} = 60.6k\Omega

ผมเริ่มต้นออกแบบโดยเลือก L6=500nm เนื่องจากเราไม่ต้องการให้ M6 มีขนาด W ที่ใหญ่เกินไป และผมได้ทำการ Sweep W เพื่อให้ได้ Vdsat อยู่ที่ประมาณ 150mV ผมจะได้ gm_6=2.095mS และ r_{ds6}=58.47k\Omega

ทรานซิสเตอร์ M7 จะถูกจำกัดโดย V_{dsat} เช่นกัน เนื่องจาก Design Specification กำหนดไว้ว่า Output Swing จะสามารถมีค่าต่ำสุดอยู่ที่ 200mV ดังนั้นเราจะเลือก V_dsat ที่ใกล้เคียงกับค่า V_dsat ของ M6 โดยเราจะเลือก L7 = 2um และทำการ Sweep ค่า Width ใน Simulation เพื่อให้ได้ค่า gm/I_d ที่ต้องการ สุดท้ายเราจะได้ r_{o7}=129.7k\Omega

จากผลลัพธ์ที่เราได้ เราสามารถคำนวณค่า Dc gain ออกมาเป็น

A_V=A_{V1}\cdot A_{V2}=A_{V1}\cdot gm_6 \cdot (r_{o6}\parallel r_{o7})=76.46dB ซึ่งมีค่าไม่ห่างจาก 80dB มากนัก

การจะเพิ่มค่ากำลังขยาย Voltage Gain ให้ได้เป็น 80dB ทำได้ไม่ยาก เราเพียงเพิ่มค่า Gm1 ด้วยการเพิ่ม Width เพียงเล็กน้อย หรือจะเพิ่ม L ของทรานซิสเตอร์ (ควบคู่กับ W เพื่อคงค่า gm) เราก็จะได้ค่าแรงดันขยายตามต้องการ

สำหรับ M5 และ Mbias เราสามารถเลือกให้มี W และ L เป็นสัดส่วนที่เท่ากับ M7 ได้ เช่น (W/L)7 = 8* (W/L)5

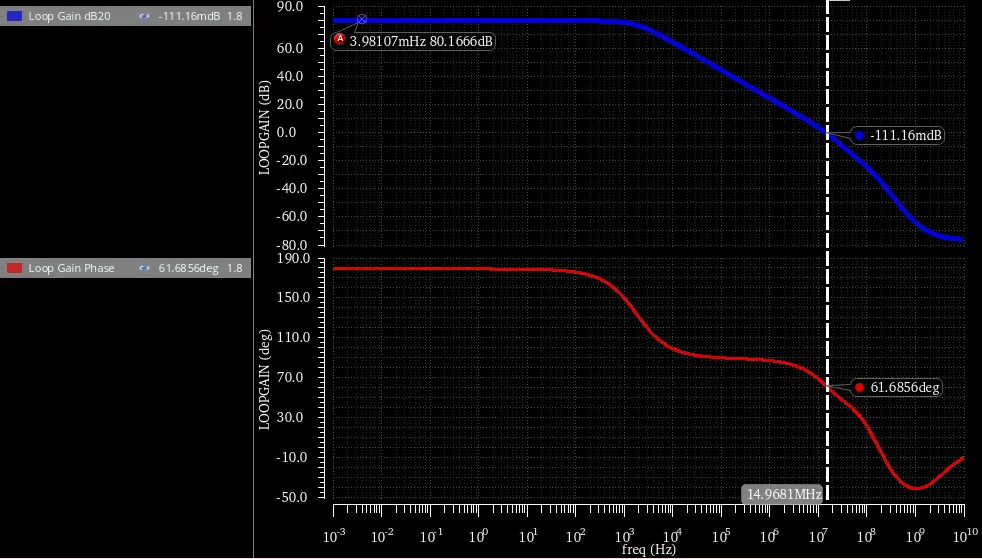

2.8). ทดสอบ Single Ended 2 Stage CMOS Opamp ที่ได้ออกแบบ

หลังจากที่เราได้ออกแบบค่า W และ L ของ Transistor แต่ละตัวแล้ว ผมก็ทำการทดสอบด้วยการรัน Stability Simulation และผมก็ได้ Loop Gain = 80dB UGBW=14.97MHz และ Phase Margin = 61.7°

สำหรับค่า Slew Rate ของ Opamp จะอยู่ที่ประมาณ 25MV/s ซึ่งใกล้เคียงกับค่าที่ออกแบบไว้ (คลาดเคลื่อนเนื่องจาก Cgs ของ M6 มีค่าที่ใหญ่พอสมควร) หากเราต้องการ Slew Rate ที่สูงขึ้น เราสามารถทำได้ง่าย ๆ ด้วยการลดค่า Cc และอาจจะเพิ่ม Rz ขึ้นมาเล็กน้อย โดยในตัวอย่าง ผมได้ทำการลด Cc เป็น 400fF และเพิ่ม Rz (ต่อ Series กับ CC) อยู่ที่ประมาณ 1kOhm และทำการ Simulate ใหม่ ผมก็จะได้ Slew Rate เพิ่มขึ้นมาอยู่ที่ประมาณ 30MV/s ตามต้องการ

แต่!! ผมแนะนำให้พยายามหลีกเลี่ยงการใช้ Rz เนื่องจากในทางปฎิบัติ R จะมีค่าแปรผันได้ถึง +/-20% หรือมากกว่านั้น ขึ้นอยู่กับขนาด และ process ซึ่งอาจทำให้ Phase Margin ที่ได้ เปลี่ยนแปลงไปอย่างมาก เมื่อเราทำการทดสอบแบบ Corner Simulation (เช่นการเปรียบเทียบกรณี Rmax, 125degree เทียบกับ Rmin -40 degress) แต่หากเราทดสอบ Corner Simulation และรับได้กับค่า Phase Margin ที่เปลี่ยนแปลงไป เราก็อาจจะใช้ Rz ได้ถ้าไม่มีทางเลือก (ผมก็ใช้ ในบางโอกาส)

เพียงแค่นี้เราก็จะได้ Single Ended Two Stage CMOS Opamp ตาม Design Specification ที่ต้องการได้ โดยใช้วิธีที่ผมได้นำเสนอ ลองเอาเทคนิคนี้ไปใช้ดู คุณจะเห็นว่าวิธีของผมทำให้เราสามารถออกแบบ Opamp ได้อย่างรวดเร็ว โดยเราสามารถใช้วิธีดังกล่าวเพื่อ Simulate ให้ได้ Opamp ตาม Spec ที่ใกล้เคียงกับสิ่งที่เราต้องการ แล้วเราค่อยๆปรับแก้ Gm และ Rout หรือแม้แต่ C เพื่อให้ได้ค่าที่เราต้องการในที่สุด

ในบทความนี้ผมได้นำเสนอวิธีออกแบบ Opamp แบบ 2 Stage ด้วย CMOS Transistor โดยผมจะผสมผสานเทคนิคการทำ Transistor Characterization ของ Borris Murmann ควบคู่กับการ Simulate and Iterate เพื่อให้ได้ผลลัพธ์ที่ต้องการอย่างรวดเร็ว

ลองนำเทคนิคนี้ไปทำตามดูนะครับ หากติดปัญหา หรือมีข้อสงสัยอะไรสามารถคอมเมนท์กันมาได้ครับ หรือส่งข้อความหาผมได้ที่ X (Twitter) และอ่านบทความเพิ่มเติมได้ที่ kangtlee.com

ผม Kang T Lee ผมเขียนบทความเกี่ยวกับ Web development, IC Design, Business and Entrepreneur และเนื้อหาที่น่าสนใจจากหนังสือที่ผมอ่าน