Current mirror เป็นบล็อคพื้นฐานที่ต้องใช้ในวงจรเกือบจะ 90% ของวงจร Analog โดยในบทความนี้เราจะสอนวิธีออกแบบ Cascode NMOS current mirror ซึ่งจะมี Rout ที่สูงมาก ๆ ซึ่งจะเหมาะสำหรับการใช้เป็น Output impedance ในวงจรขยาย เช่นวงจร Opamp

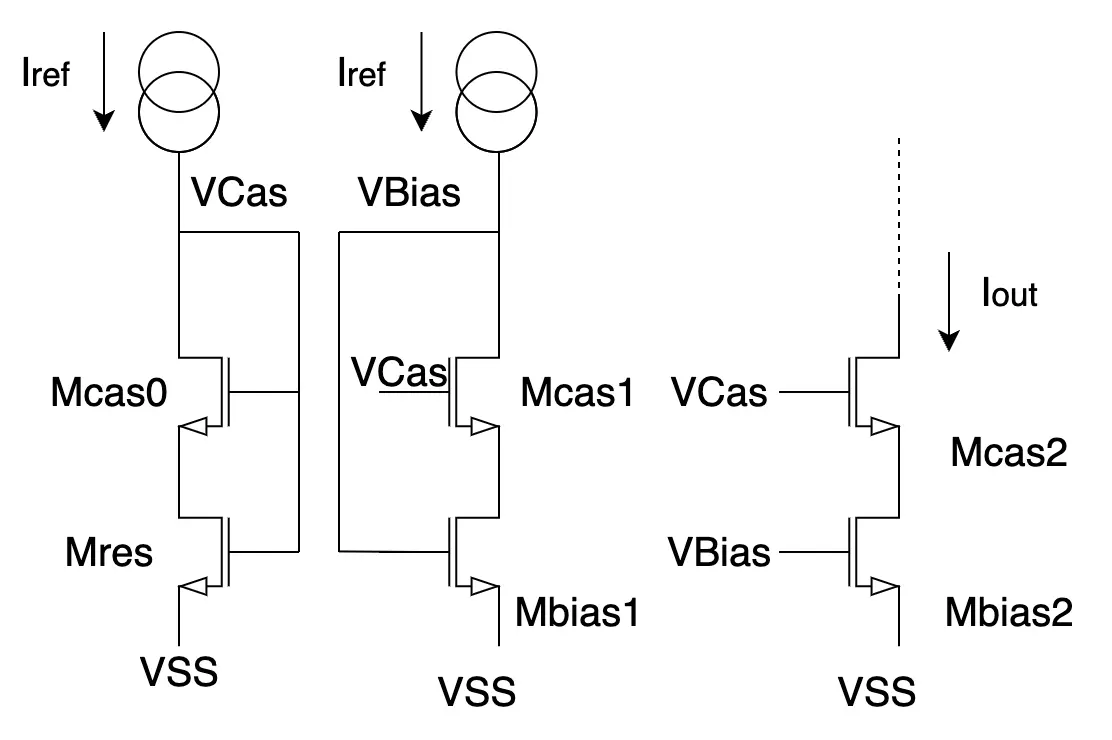

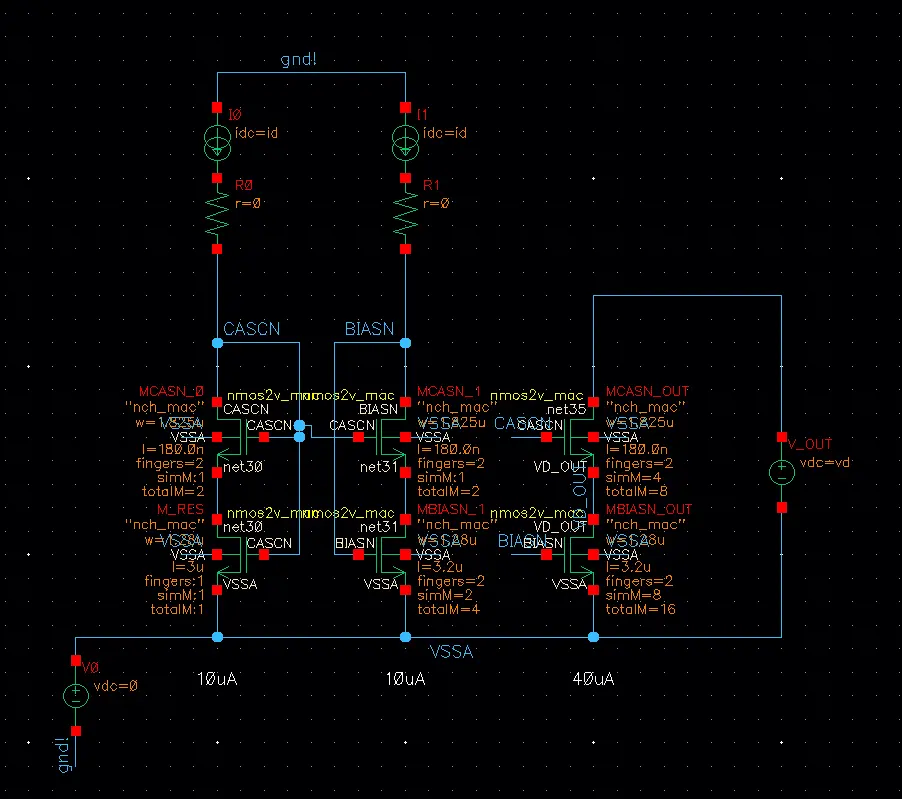

วงจรที่จะใช้ในการออกแบบ NMOS cascode current mirror จะเป็นดังรูป โดยเราต้องป้อนแรงดัน VBias ให้เท่ากับ

V_{Bias} = V_{TH,Mbias2}+V_{dsat,Mbias2}

และแรงดัน VCas เท่ากับ

V_{Cas}=V_{dsat,MBias2}+V_{dsat,MCas2}+V_{TH,MCas2}

โดยเราจะได้ความต้านทาน Rout ของวงจร Cascode current mirror อยู่ที่

R_{out}=r_{Mcas2}+r_{Mbias2}+gm_{Mcas2}\cdot r_{Mcas2} \cdot r_{Mbias2}\approx gm_{Mcas2}\cdot r_{Mcas2} \cdot r_{Mbias2}

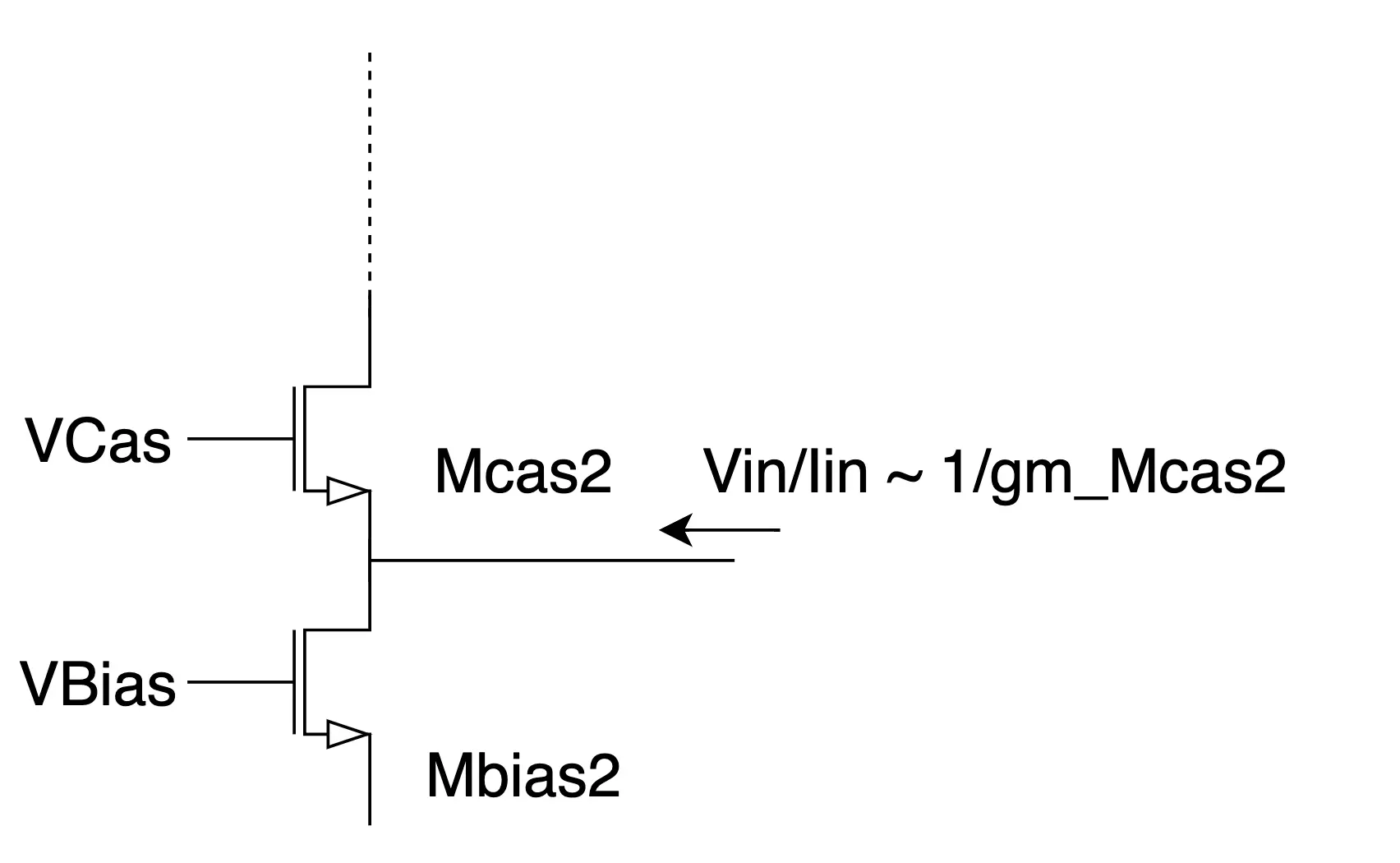

หากเราพิจารณาวงจร Cascode current mirror เราจะพบว่าตัว Cascode transistor (MCas2) ทำหน้าที่เป็น gm cell ที่จะช่วยทำให้ Vdrain ของ Mbias2 มีค่าคงที่จากผลของ Negative feedback ซึ่งจะทำให้ Rin ที่ Drain ของ Mbias2 มีค่าประมาณ 1/gm_{Mcas2} ซึ่งทำให้ Vdrain มีค่าคงที่แม้จะมีการเปลี่ยนแปลงของแรงดัน Vdrain ที่ Mcas2 เกิดขึ้นนั่นเอง โดยความสามารถในการกด Drain voltage ให้คงที่จะขึ้นอยู่กับขนาดของ gm

จากข้อสังเกตดังกล่าว เราจะต้องออกแบบให้ Mcas2 มีค่า gm ที่สูง โดยเราจะเลือก gm/id อยู่ที่ประมาณ 15-20 ในขณะที่ Mbias2 จะมีค่า gm/id อยู่ที่ประมาณ 5-10 เพื่อให้เราได้ over-drive voltage ที่สูงเพื่อลด current mismatch (อ่านเพิ่มได้ที่นี่)

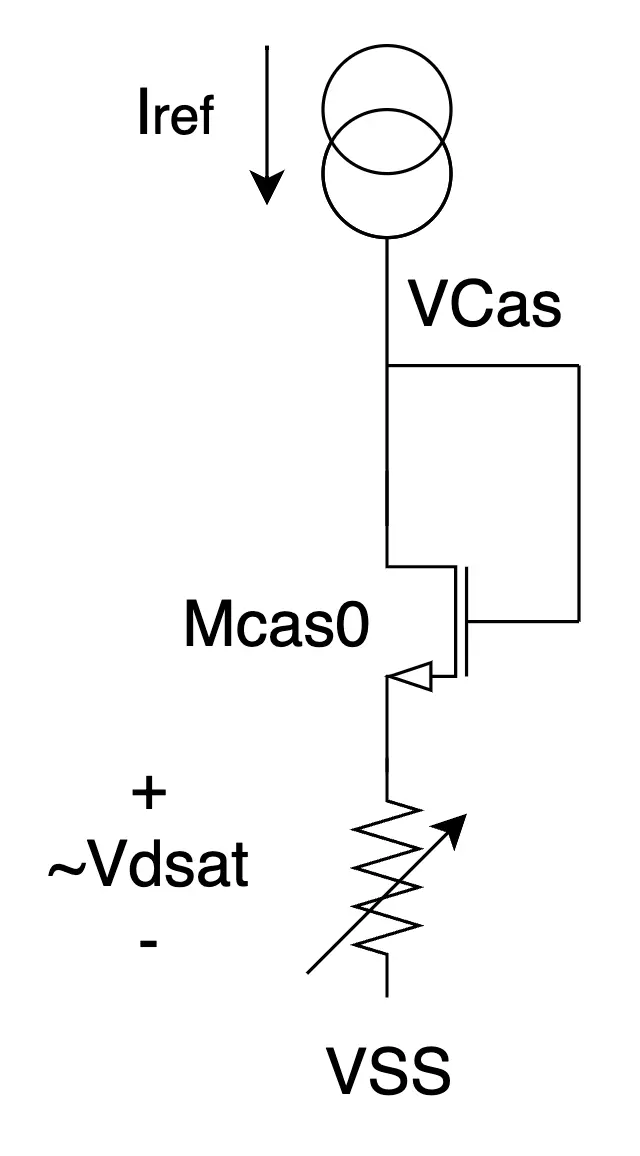

และสำหรับแรงดันไบอัสสำหรับ Cascode current mirror เราจะทำการสร้างแรงดัน VCas ด้วยวงจรดังรูปข้างล่าง โดยเราจะต้องเลือก R เพื่อสร้างแรงดันให้มีค่าเท่ากับ Vdsat_Mbias2 นั่นเอง โดยจะเห็นว่าเราใช้ NMOS ต่อเป็น Resistor (ทำงานใน Linear region, Vds<Vdsat) เพราะในการออกแบบ Layout เราสามารถวาง MOS ในตำแหน่งใกล้กัน เพื่อให้ได้รับผลของ Process and Temerature variation ที่ใกล้เคียงกัน

ในตัวอย่างนี้เราต้องการออกแบบ Current mirror ที่มีความต้านทาน Rout = 10MOhm มีกระแสอยู่ที่ 40uA และมี Vd ต่ำสุดอยู่ที่ 400mV และในการออกแบบครั้งนี้เราจะใช้หลักการ MOS characterization ที่เคยได้เสนอในบทความนี้

เราเริ่มต้นด้วยการออกแบบ Mbias2 ด้วยการเลือก Vov=250mV ซึ่งเราจะได้

\frac{gm}{I_d}=\frac{2}{V_{ov}}=8

และ gm อยู่ที่

gm=\frac{gm}{I_d}\cdot I_d=8 \cdot 40uA=320uS

และเราสามารถหาค่า instrinsic gain อยู่ที่

\frac{gm}{gds}=gm\cdot rds=320uS \cdot 1M\Omega=320

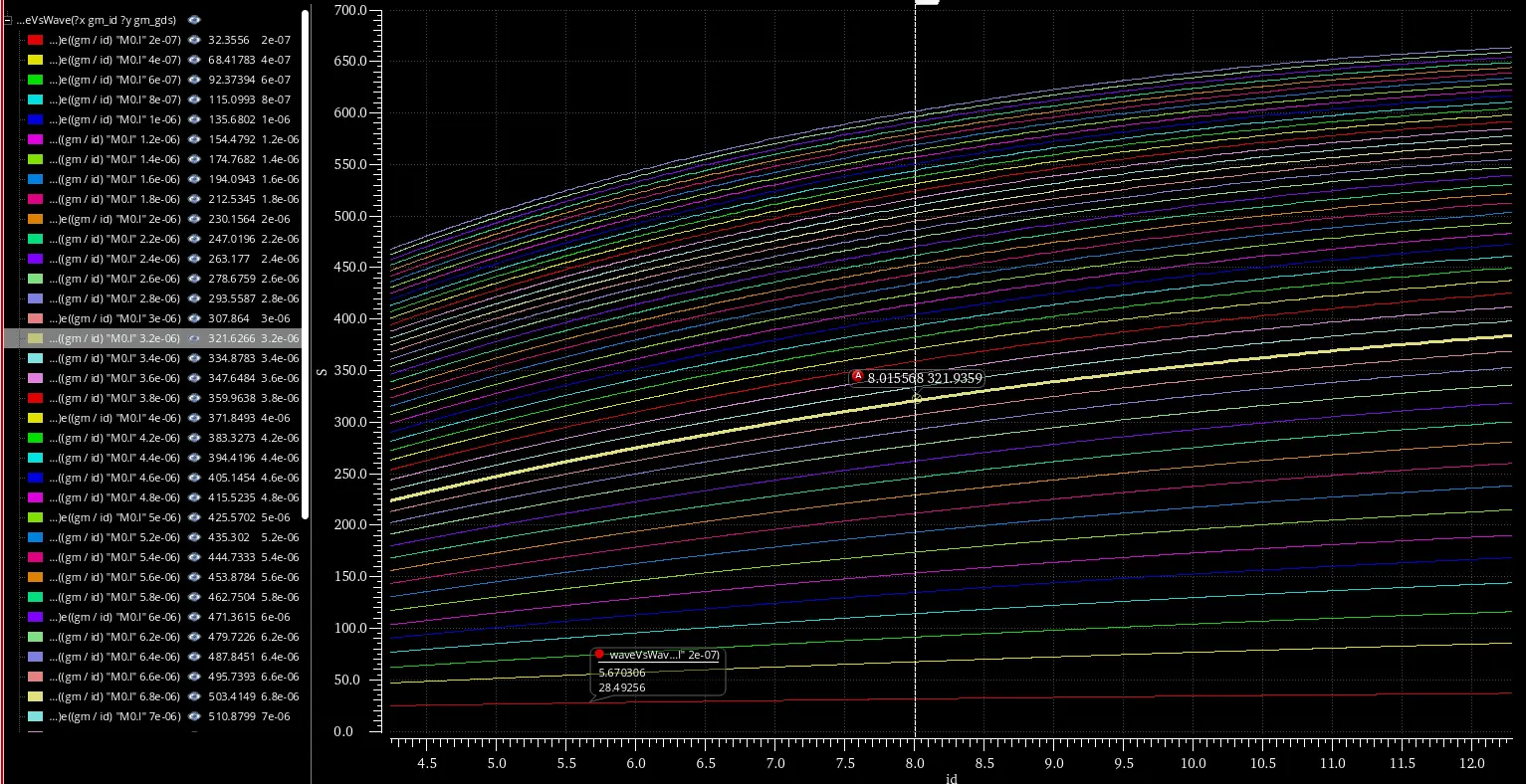

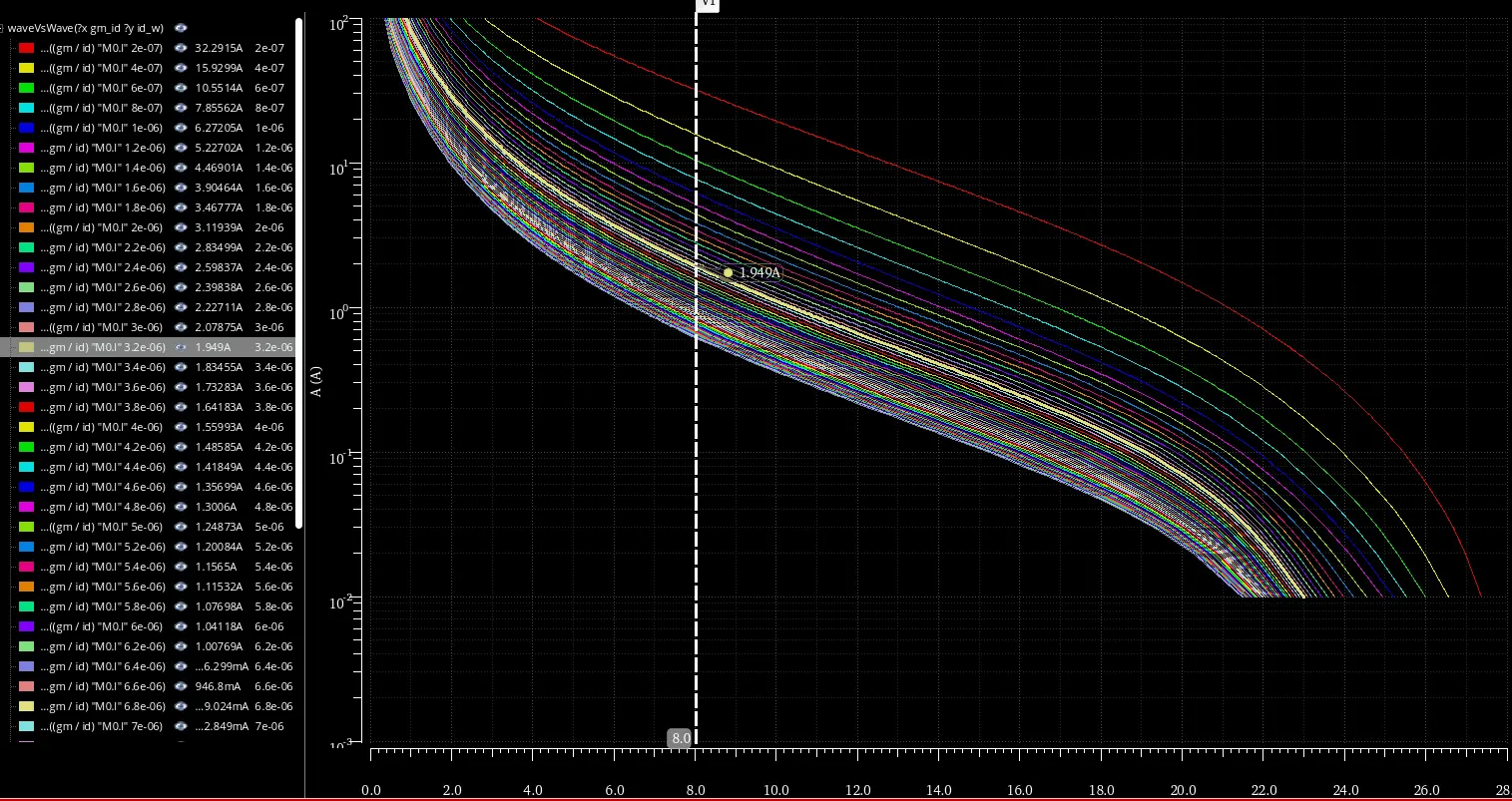

จากกราฟ Intrinsic Gain เราค้นหา L ที่ทำให้ได้ค่า gm/id=8 และ gm/gds=320 ซึ่งจะทำให้เราได้ L=3.2um ดังกราฟข้างล่าง

เมื่อเราได้ L ของ Transistor เราก็จะสามารถหาค่า W ได้จากกราฟ Current density โดยเลือกกราฟที่มี L = 3.2um ที่ gm/id=8 เราจะได้ Id/W=1.949 ดังรูป

ซึ่งจะทำให้เราได้

W=\frac{Id}{Id/W}=40uA/1.949=20.5um

หลังจากนั้นเราจะทำการออกแบบ Mcas โดยการเลือก gm/id=18 ซึ่งจะทำให้เราได้ Vov=111mV นั่นเอง โดยเราจะได้ V_{ov,bias} + V_{ov,cas} = 111mV + 250mV < 400mV

จาก gm/id=18 และ Id=40uA เราจะได้ gm=720uS

จากนั้นเราจะหาค่า rds ของ Mcas จากสมการ

R_{out}\approx gm_{Mcas2}\cdot r_{Mcas2} \cdot r_{Mbias2}

r_{Mcas2}=\frac{R_{out}}{gm_{Mcas2}\cdot r_{Mbias2}}=\frac{10M\Omega}{720\mu S \cdot 1M\Omega}=13.89k\Omega

และเราจะได้ Intrinsic gain

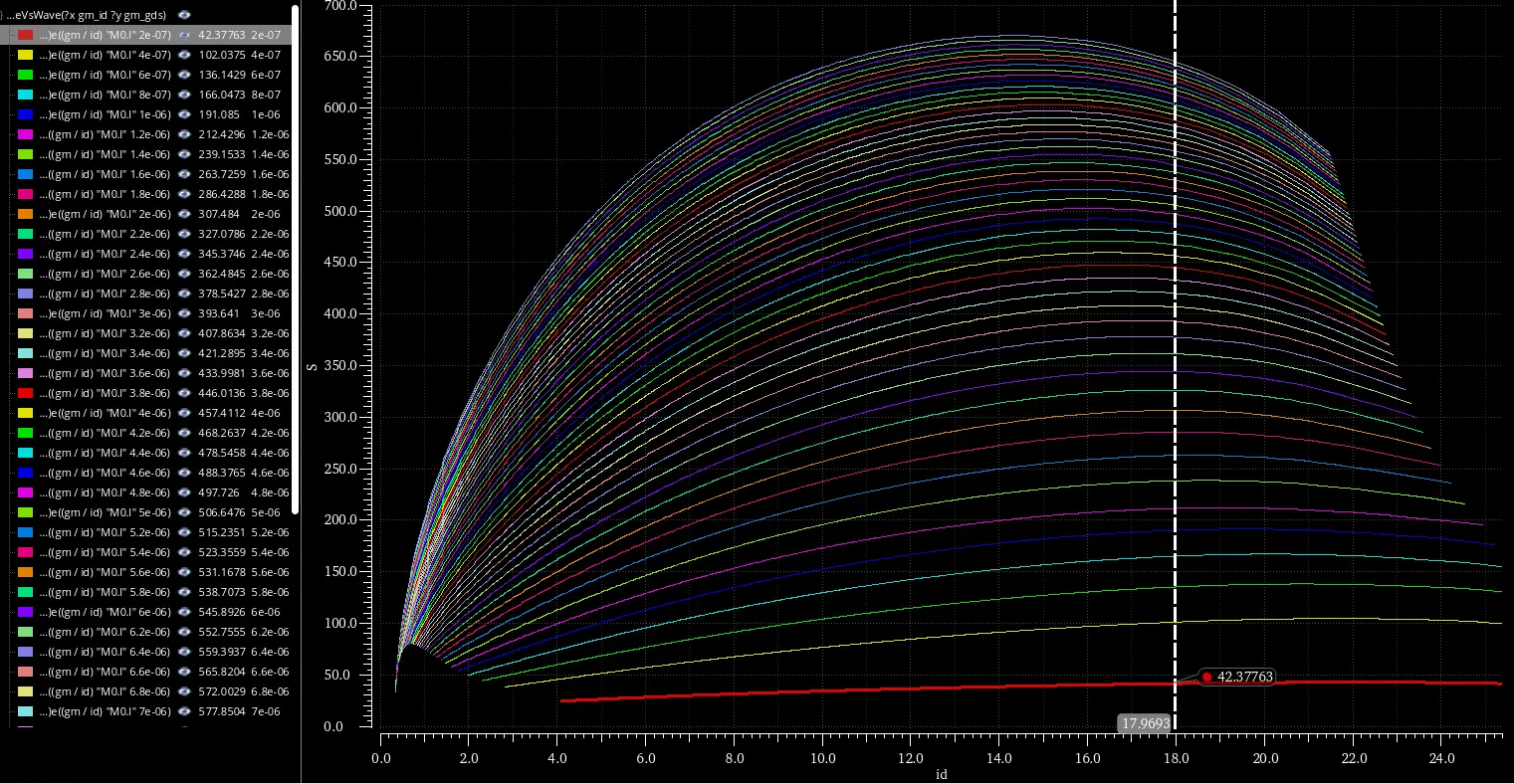

gm/gds=10

โดยเราจะเลือก L=180nm ดังรูปข้างล่าง และเราจะได้ W=14.6um จากกราฟ Current densitry (ใช้วิธีเดียวกับกราฟข้างบน)

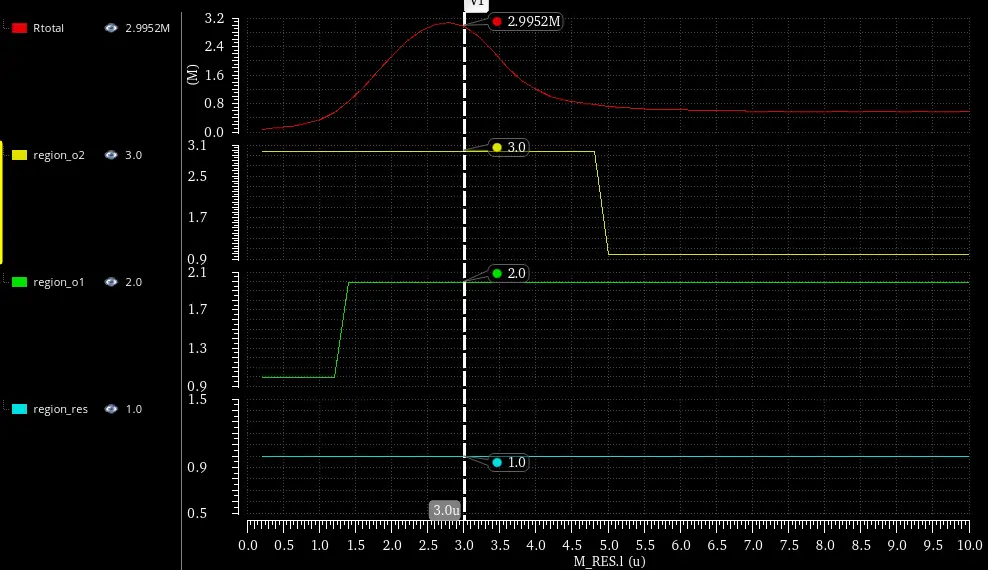

หลังจากนั้นเราจะต้องทำการหาค่า Width และ Length ของ Mres โดยเราจะทำการ Simulate โดยการ Sweep ค่า L ของ Mres โดยเลือก W_mres = 1.28um ดังรูปวงจรดด้านล่าง โดยเราจะป้อนกระแส Iref อยู่ที่ 10uA เข้าสู่ Drain ของ MCAS_0 และ MCAS1 และทำการวัด Rtotal ของวงจรจาก MBIASN_OUT และ MCASN_OUT ที่ Vd=0.9V (Vdd/2) และ Vd=0.4V

ใน ADE เราจะเซฟค่าผลลัพธ์ใน ADE XL > Outpus > Setup โดยเราจะเซฟตัวแปรดังนี้

rds_o1 ⇒ 1 / pv(”MBIASN_OUT” “gds” ?result “dcOpInfo”)

rds_o2 ⇒ 1 / pv(”MCASN_OUT” “gds” ?result “dcOpInfo”)

gm_o2 ⇒ 1 / pv(”MCASN_OUT” “gm” ?result “dcOpInfo”)

Rtotal ⇒ rds_o1 + rds_o2 + (gm_o2 rds_o1 r_dso2)

region_o1 ⇒ pv(”MBIASN_OUT” “region” ?result “dcOpInfo”)

region_o2 ⇒ pv(”MCASN_OUT” “region” ?result “dcOpInfo”)

region_res ⇒ pv(”M_RES” “region” ?result “dcOpInfo”)

โดย region จะเป็นค่า Operation region ของตัว Transistor ซึ่งจะมีค่าเป็น:

region=0 ⇒ cut-off

region=1 ⇒ triode / linear

region=2 ⇒ saturation

region=3 ⇒ subthreshold

region=4 ⇒ breakdown

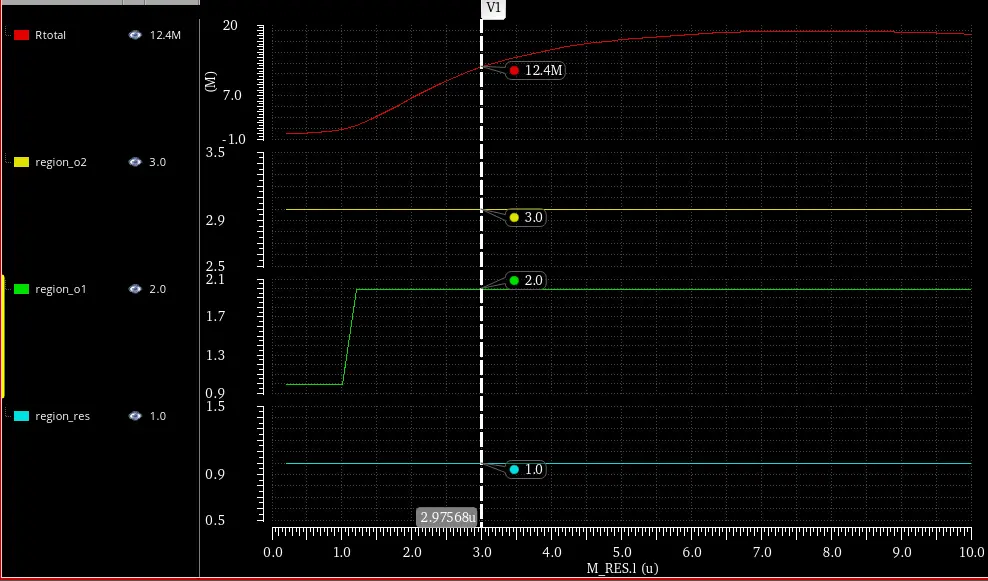

ที่แรงดัน Vdrain = 0.9V เราจะได้ผลของ Rout จากการกวาด Length ของ MRes ดังรูป

และที่แรงดัน Vdrain = 0.4V เราจะได้ผลของ Rout จากการกวาด Length ของ MRes ดังรูป

สังเกตจากกราฟผลลัพธ์เมื่อ Vd=400mV เมื่อ L มีค่าสูงขึ้น เราจะได้ Rout ที่ลดลง เนื่องจากเมื่อ L มีค่าสูงขึ้นจะทำให้ Vcas มีค่าสูงขึ้น นั่นหมายความว่า Vd_min ที่จะทำให้ Mcas อยู่ในสถานะ Saturation region มีค่าแรงดันที่สูงขึ้นนั่นเอง และการป้อนแรงดัน Vdrain ให้อยู่ที่ 400mV จะทำให้ Mcas ไม่อยู่ในสถานะ Saturation อีกต่อไป และทำให้ gm ที่ได่มีค่าต่ำมากๆ นั่นจึงทำให้ Rout มีค่าที่ต่ำลงไปด้วยนั่นเอง

และจากผลลัพธ์ของ DC simulation เราจะเลือก L ของ Mres อยู่ที่ 3um ซึ่งจะทำให้เราได้ Rout อยู่ที่ประมาณ 10MOhm

ในบทความนี้เราได้สอนวิธีออกแบบ NMOS cascode current mirror โดยใช้วิธี MOS characterization ด้วยการดู Pre-computed lookup table ที่ได้เสนอในบทความนี้ และเราได้แสดงตัวอย่างการออกแบบวงจรรวมถึงการ Simulate เพื่อหาค่า Rout ของวงจร Cascode current mirror ที่ต้องการ

ผม Kang T Lee ผมเขียนบทความเกี่ยวกับ Web development, IC Design, Business and Entrepreneur และเนื้อหาที่น่าสนใจจากหนังสือที่ผมอ่าน