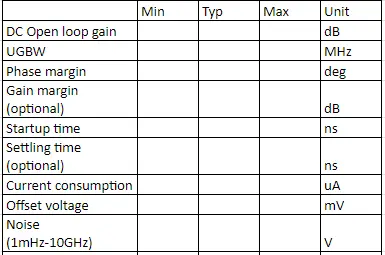

บทความนี้จะสอนวิธี simulate วงจรออปแอมป์ (Opamp) บน Cadence Virtuoso เพื่อทดสอบประสิทธิภาพของวงจร Opamp ที่เราออกแบบ โดย Parameters ที่เราสนใจจะมาจาก Design Specification ดังนี้

DC Loop gain

UGBW

Phase margin

Gain margin

Settling time

Startup time

Current consumption

Offset voltage

Noise

จาก Design Specification ทั้งหมดของออปแอมป์ เราจะได้ตารางดังรูปข้างล่าง

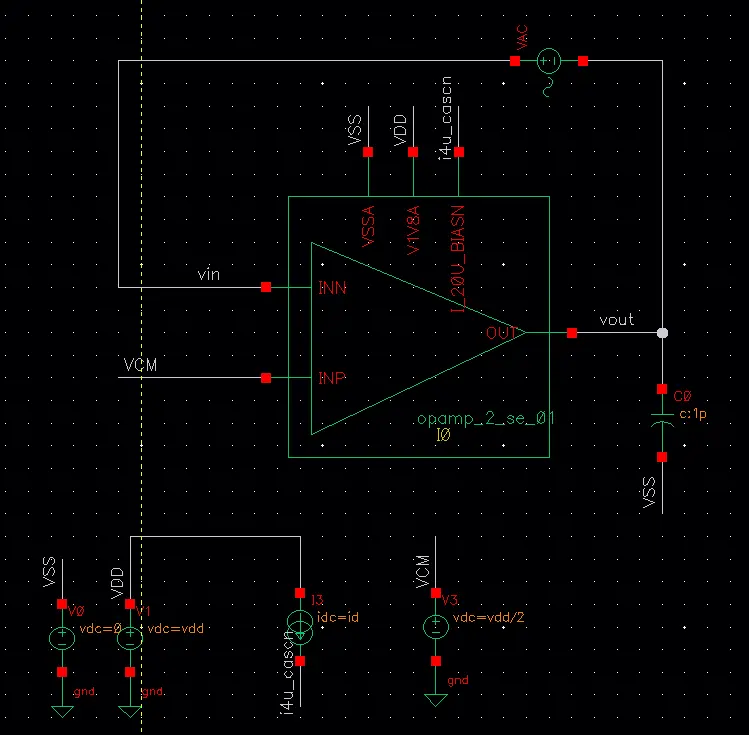

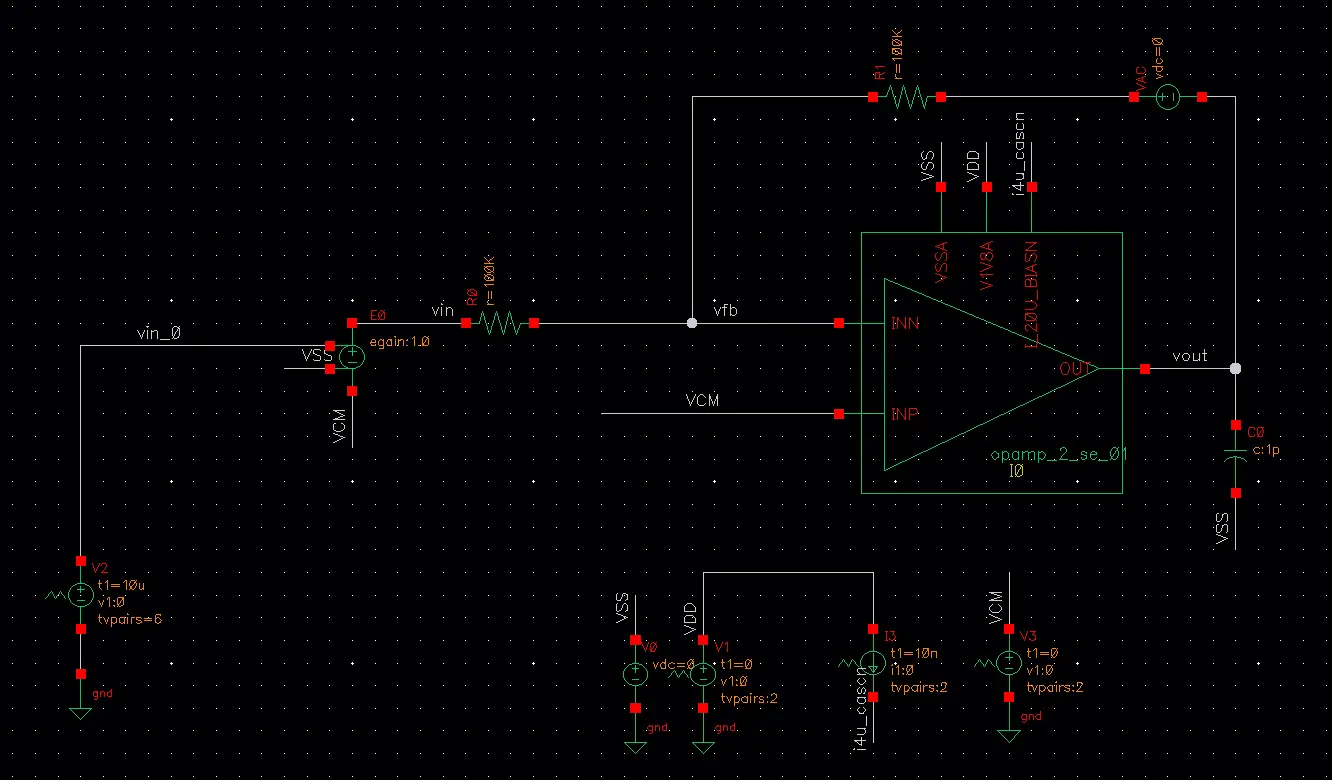

เราเริ่มจากการ simulate Stability Analysis ด้วยการต่อวงจรดังรูป โดยเราจะใช้ vdc source ต่อระหว่าง feedback path ของวงจรออปแอมป์โดยให้ขั้วบวกอยู่ตำแหน่งอินพุทของและขั้วลบอยู่ตำแหน่งเอาท์พุทของออปแอมป์ การต่อวงจรและ simulate ด้วย Stability Analysis จะมีข้อดีกว่าการ simulate แบบ AC Analysis เพราะเราสามารถ simulate วงจรด้วยการต่อวงจรแบบป้อนกลับเพื่อเอาท์พุทของวงจรได้รับผลกระทบการ input parasic capacitance ด้วย

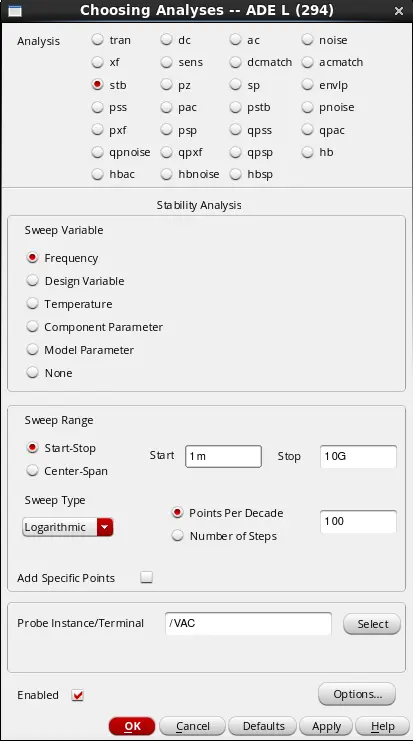

เราจะตั้งค่า Stability Analysis ใน ADE ดังรูป โดยเราต้องเลือก Probe Instance ที่เป็น Voltage Source ที่ต่อใน Feedback path

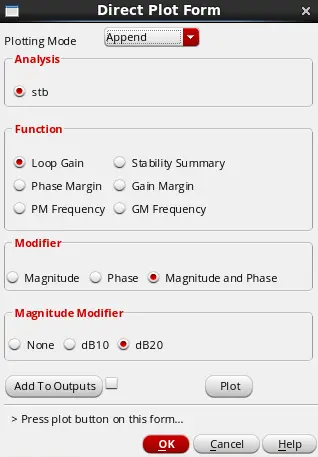

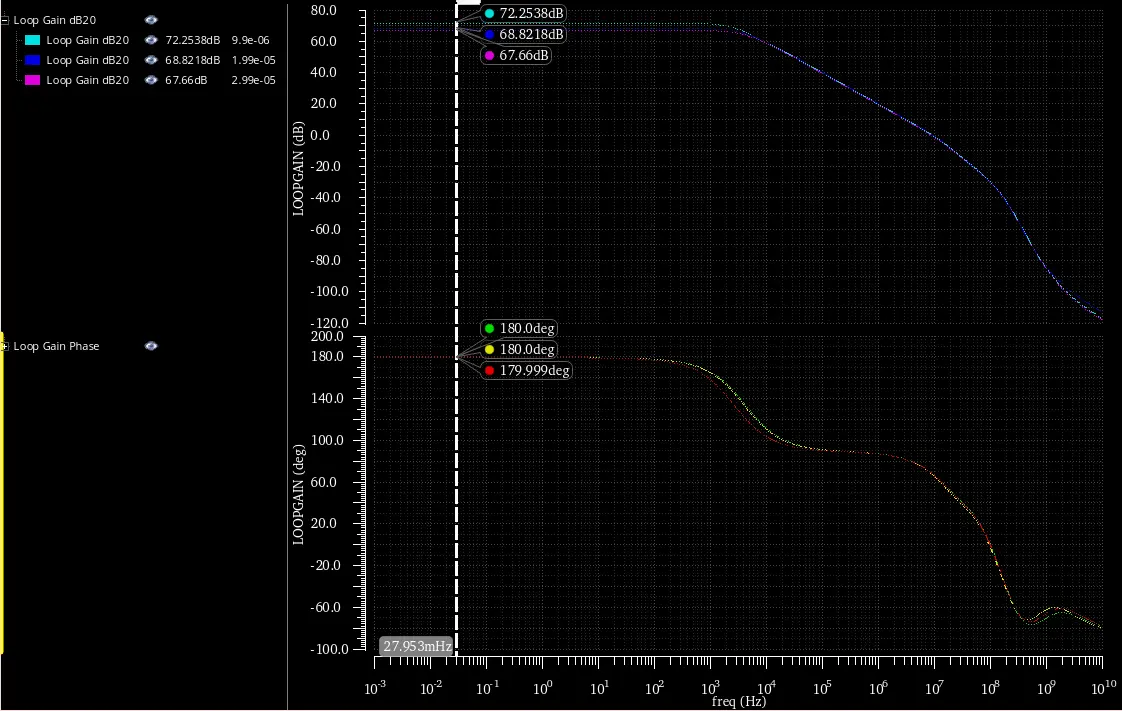

หลังจากที่การรัน Simulation เสร็จสิ้น เราสามารถตรวจสอบผลลัพธ์ของ Stability Analysis ได้จาก ADE > Results > Direct Plot > Main Form เราจะสามารถพล็อตกราฟ Frequency Response เพื่อให้ Open Loop Gain, Unity Gain Bandwidth, Phase Margin และ Gain Margin ได้ดังรูป

กรณีที่เราต้องการ Run Stability Analysis ขณะที่วงจรกำลังทำงาน เช่น ในวงจร Switch-capacitor ที่ไม่สามารถรันจาก DC Operating Point นั้น เราสามารถ Run PSS (Periodic Steady-State Analysis) และ PAC เพื่อให้ได้ Frequency Response แต่วิธีดังกล่าวจะใช้เวลานานเนื่องจาก Spectre ต้องคำนวณหา Steady state condition ของวงจร

วิธีที่เร็วกว่านี้ คือการทดสอบด้วยการทำ Transient Simulation ควบคู่กับ Stability Analysis โดยตัว Spectre จะทำการดึง DC Operating Point จาก Transient Simulation ณ เวลาที่เรากำหนด โดยเราจะ Setup วงจรดังตัวอย่างตามรูปข้างล่าง

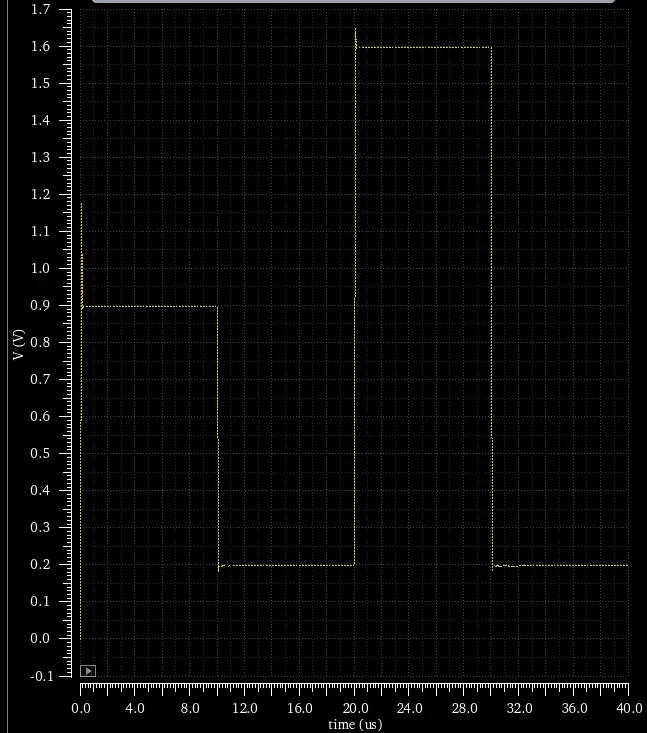

จากรูป เราจะต่อวงจรแบบป้อนกลับ และป้อนแรงดันเพื่อให้ Vout มีค่าสามระดับ นั่นคือ Vout = Vcm, Vout = Vmin และ Vout = Vmax เพื่อจะหา Loop Gain ที่ Voltage ระดับต่าง ๆ โดยเราจะได้แรงดันเอาท์พุทดังรูปข้างล่าง

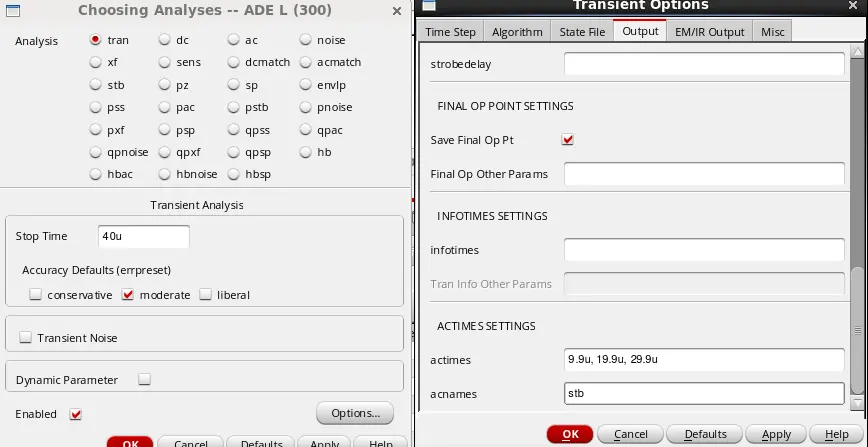

โดยเราจะตั้งค่า Transient Analysis ดังรูปข้างล่าง โดยจะเห็นว่าเราจะ Run Stability Analysis ที่เวลา t=9.9us, 19.9us และ 29.9us เนื่องจากเป็นเวลาที่ Vout อยู่ที่ 0.9V, 0.2V และ 1.6V

เมื่อเราตรวจสอบผลลัพธ์ เราจะได้ Frequency Response ตามเวลาที่ได้ที่การ Run Stability Analysis ดังรูป

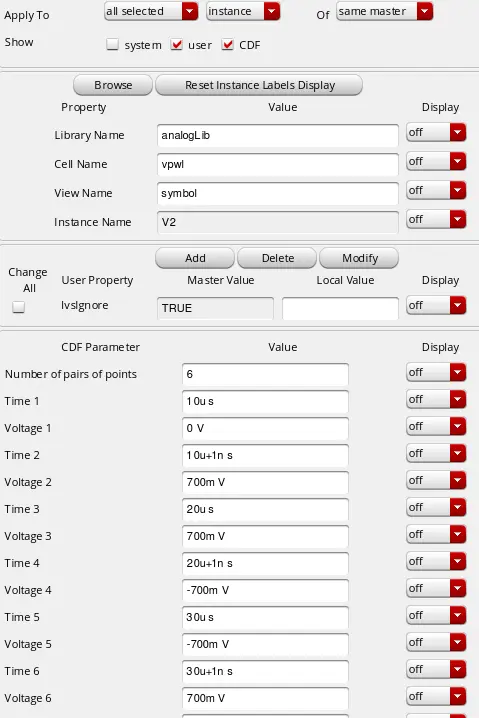

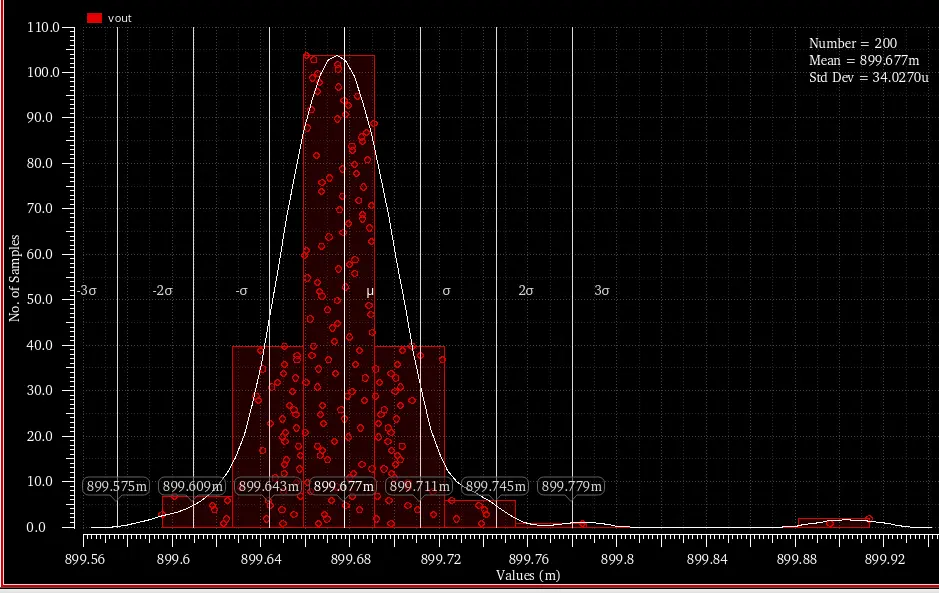

เราสามารถทดสอบวงจรเพื่อหาค่า Settling time, Startup time และ Slew rate ของวงจรออปแอมป์ได้โดยการทดสอบ Transient Simulation โดยในตัวอย่าง เราจะป้อนแรงดันโดย vpwl ดังรูปข้างล่าง ที่อินพุท (V2) และ Supply (V1)

จากนั้น ที่ ADE Output > Setup เราจะทำการบันทึก Slew Rate Rise และ Fall ด้วยสมการเช่น

slew_rise = slewRate(clip(VT(”/vout”) 1.8e-05 2.2e-05) 0.2 nil 1.6 nil 20 80 nil “time”)

slew_fall = -slewRate(clip(VT(”/vout”) 28u 32u) 1.6 nil 200m nil 20 80 nil “time”)

ในตัวอย่างสมการ Slew Rate เราจะพล็อต Vout ในช่วงเวลาสองช่วง ระหว่าง 18us ถึง 22us และระหว่าง 28us ถึง 32us เนื่องจากเป็นเวลาที่แรงดันมีการเปลี่ยนแปลงจาก Low to High จาก 0.2V to 1.6V และ High to Low จาก 1.6V to 0.2V โดยเราจะวัดค่า Slew rate ในช่วง 20-80%

และตัวแปร Settling time จากตัวอย่างสมการ

settling_time = settlingTime(clip(VT(”/vout”) 9u 19.9u value(VT(”/vout”) 9u) nil 200m nil 0.1 nil “time”)-10u

(สังเกตว่าเราใส่ -10us เนื่องจากแรงดันเอาท์พุทเกิดการเปลี่ยนแปลงที่เวลาประมาณ 10us)

ในตัวอย่างสมการ เราเลือก 0.1% ของ 200mV เป็น error ที่เรายอมรับ

และสมการสำหรับ startup time เราจะบันทึกด้วยสมการ

startup_time = settlingTime(clip(VT(”/vout”) 0 9u 0 nil 0.9 nil 1 nil “time”)

โดยในตัวอย่าง เราจะบันทึกเวลาที่แรงดัน Settle ที่ 0.9V โดยมี Error อยู่ที่ 1%

เราสามารถบันทึกค่า Offset Voltage และ Current consumption ได้จาก DC simulation หรือจาก Transient Simulation ก็ได้

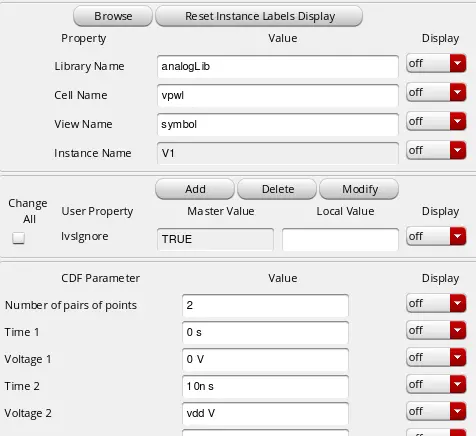

และสำหรับ Offset Voltage เราต้องการหาค่า standard deviation ของแรงดัน โดยจะมีสองวิธีที่เราสามารถทดสอบได้ คือ 1) DC Device Matching Analysis ซึ่งจะมีความเร็วในการทดสอบ แต่อาจไม่แม่นยำเท่า และ 2) Monte Carlo Simulation ซึ่งจะมีความแม่นยำกว่า แต่จะใช้เวลานานกว่าในการทดสอบวงจร โดยเราสามารถตั้งค่าเพื่อทดสอบ Monte Carlo Simulation บน ADE XL ได้ดังรูป

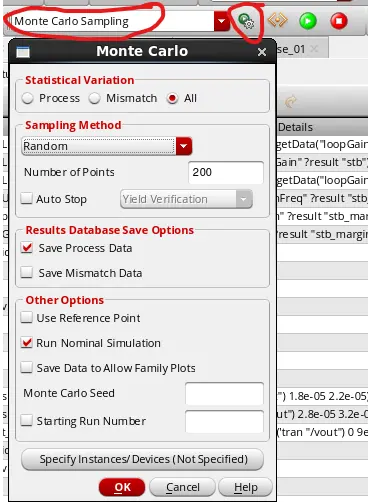

เราจะได้ผลลัพธ์ของ Offset Voltage ที่มี sigma = 34.02uV ดังรูป (โดยทั่วไปเราอาจจะบันทึก Offset ที่ +/-3*sigma หรือ 6*sigma ขึ้นกับความต้องการของ Application)

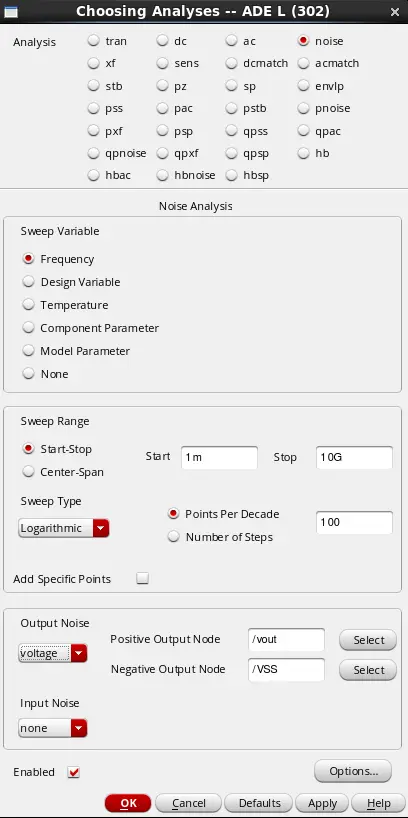

เราสามารถทดสอบเพื่อหา Input Noise ของวงจรออปแอมป์ได้สองวิธี คือ 1) AC Noise Analysis ซึ่งจะมีความรวดเร็วในการทดสอบ แต่ไม่สามารถทดสอบกับวงจรประเภท Switching Circuit ได้ และ 2) Transient Noise Analysis โดยในตัวอย่างนี้เราจะทดสอบด้วยการ Run AC Noise Analysis ด้วยการตั้งค่าใน ADE ดังรูป

จากนั้นเราจะแสดงผลลัพธ์ของการทดสอบจาก ADE > Results > Direct Plot > Squared Output Noise เราจะได้กราฟแสดง Output Noise หน่วย V^2/Hz โดยเราจะใช้ Calculator ทำการ Integrate ในช่วงความถี่ที่สนใจ เช่นระหว่าง 1mHz และ 10GHz และทำการ square root เพื่อให้ได้ Output Noise ที่ต้องการ

Output noise = sqrt( integ ( VN2(…) ) )

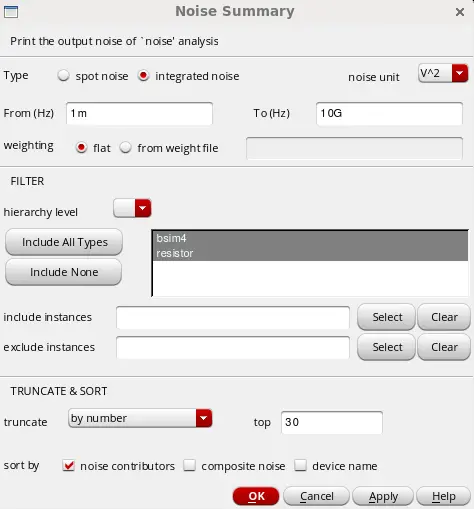

นอกจากนี้ เรายังสามารถแสดงค่า Noise contribution จาก Device ต่างๆที่ใช้ในวงจรได้ ด้วยการเลือก ADE > Results > Print > Noise Summary โดยเราจะเลือกค่าดังรูปข้างล่าง

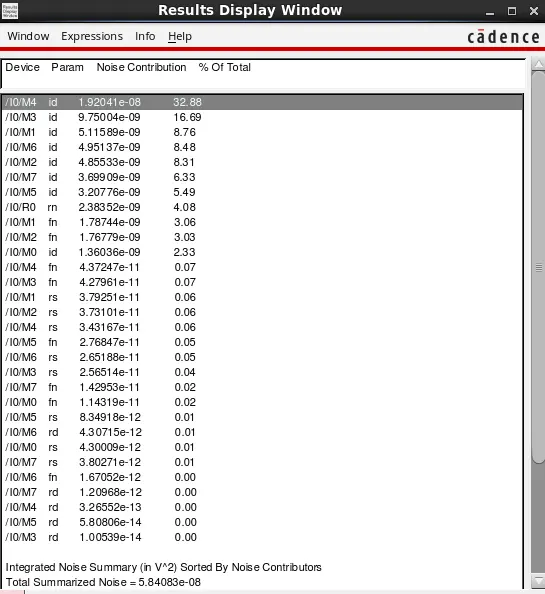

เราจะได้ผลลัพธ์ดังรูปข้างล่าง จากตัวอย่าง เราจะเห็นว่า Noise ประมาณ 30% มาจากทรานซิสเตอร์ M4 ในวงจร Transistor ดังนั้นหากเราต้องการปรับปรุงวงจรเพื่อลด Noise เราสามารถเปลี่ยนแปลงค่าตัวแปรของ Transistor ที่ส่งผลต่อ Noise มากที่สุดได้

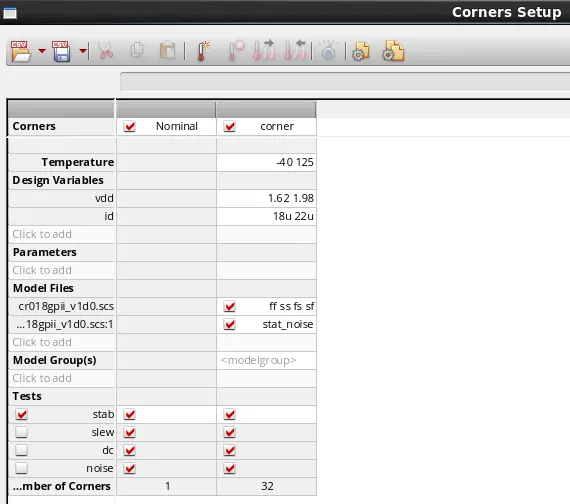

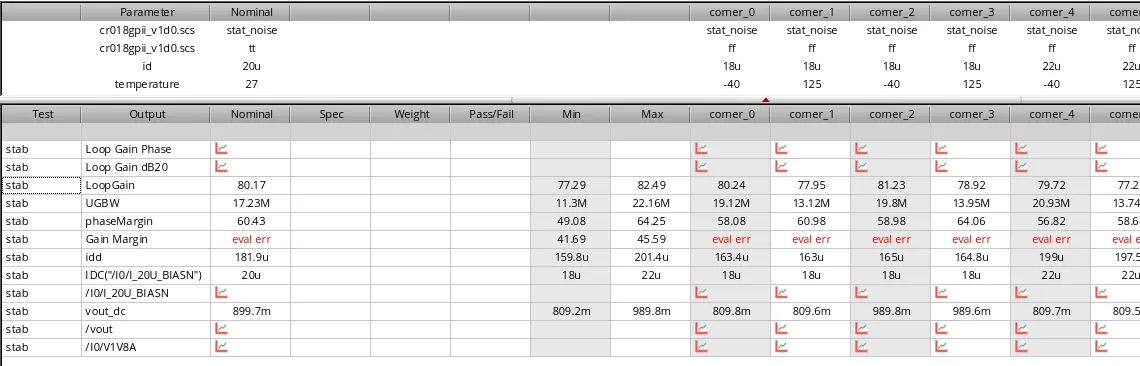

หลังจากที่เรา Setup การ Simulate วงจรเพื่อให้ได้ Design Specification ที่เราสนใจ เราจะทำการทดสอบ Corner Simulation เพื่อให้ได้ Best and Worst case ของ Design Specification เช่นค่า Minimal, Typical and Maximum UGBW โดยเราจะต้องปรับค่า Temperature (เช่นระหว่าง -40 - 125 องศา), ค่าแรงดัน Supply (เช่น +/- 10% ของ VDD) ค่ากระแสไบอัส (เช่น +/- 10% ของ I Reference), ค่า Process ของ NMOS, PMOS, Resistor, Capacitor และ BJT (ถ้ามี) เช่นตัวอย่าง Corner Setup ใน ADE XL ดังรูป

เราจะได้ตัวอย่างผลลัพธ์ดังรูป

ในบทความนี้เราได้แสดงวิธีการ Setup วงจรออปแอมป์เพื่อทำการทดสอบแบบ Simulation เพื่อให้ได้ค่า Design Specifications ของวงจรที่เราออกแบบ

ผม Kang T Lee ผมเขียนบทความเกี่ยวกับ Web development, IC Design, Business and Entrepreneur และเนื้อหาที่น่าสนใจจากหนังสือที่ผมอ่าน